Table 28 – Xilinx DS610 User Manual

Page 35

Spartan-3A DSP FPGA Family: DC and Switching Characteristics

DS610 (v3.0) October 4, 2010

Product Specification

35

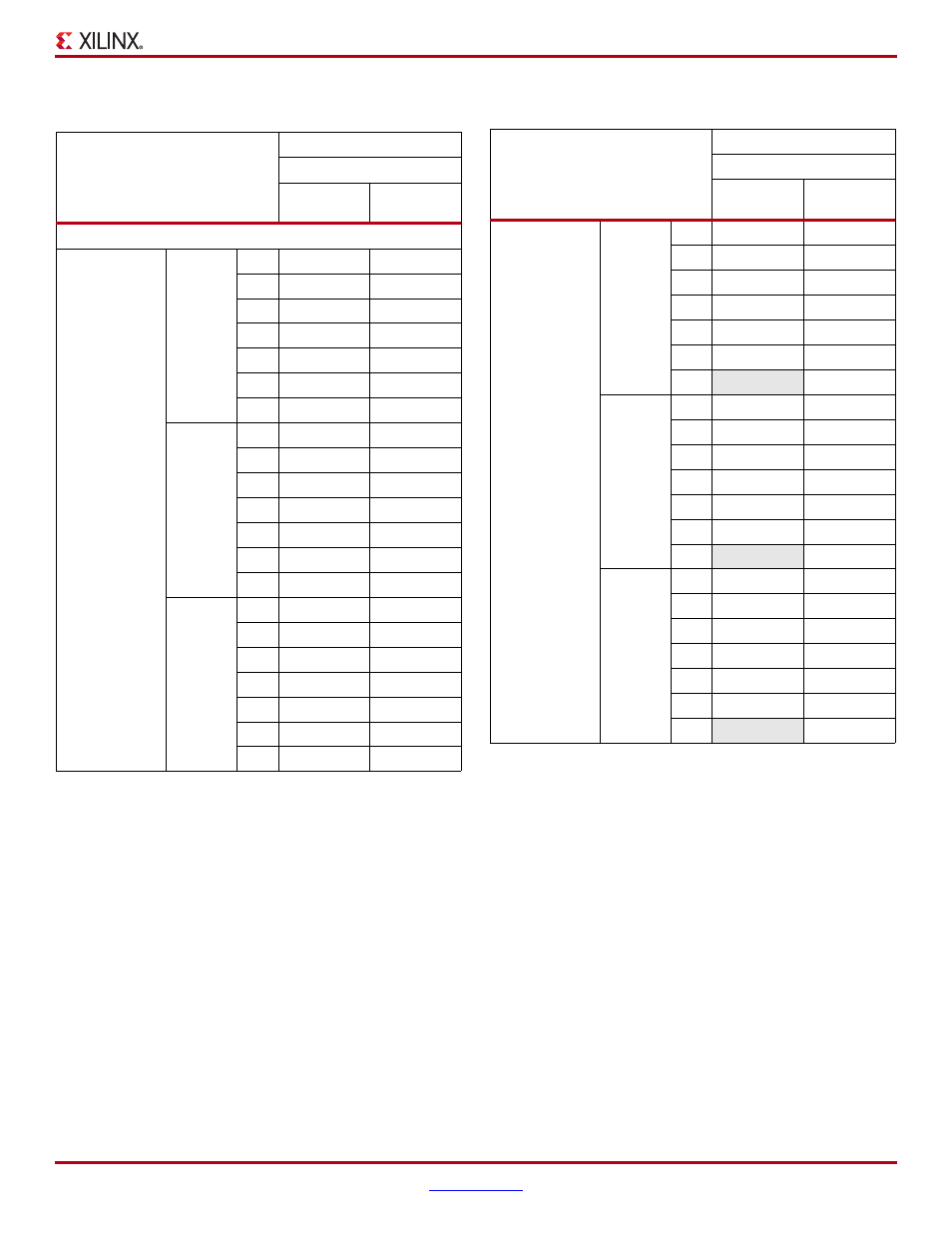

Table 28: Recommended Simultaneously Switching

Outputs per V

CCO

/GND Pair (V

CCAUX

= 3.3V)

Signal Standard

(IOSTANDARD)

Package Type

CS484, FG676

Top, Bottom

(Banks 0, 2)

Left, Right

(Banks 1, 3)

Single-Ended Standards

LVTTL

Slow

2

60

60

4

41

41

6

29

29

8

22

22

12

13

13

16

11

11

24

9

9

Fast

2

10

10

4

6

6

6

5

5

8

3

3

12

3

3

16

3

3

24

2

2

QuietIO

2

80

80

4

48

48

6

36

36

8

27

27

12

16

16

16

13

13

24

12

12

LVCMOS33

Slow

2

76

76

4

46

46

6

27

27

8

20

20

12

13

13

16

10

10

24

–

9

Fast

2

10

10

4

8

8

6

5

5

8

4

4

12

4

4

16

2

2

24

–

2

QuietIO

2

76

76

4

46

46

6

32

32

8

26

26

12

18

18

16

14

14

24

–

10

Table 28: Recommended Simultaneously Switching

Outputs per V

CCO

/GND Pair (V

CCAUX

= 3.3V) (Cont’d)

Signal Standard

(IOSTANDARD)

Package Type

CS484, FG676

Top, Bottom

(Banks 0, 2)

Left, Right

(Banks 1, 3)