Revision history – Xilinx DS610 User Manual

Page 61

Spartan-3A DSP FPGA Family: DC and Switching Characteristics

DS610 (v3.0) October 4, 2010

Product Specification

61

Revision History

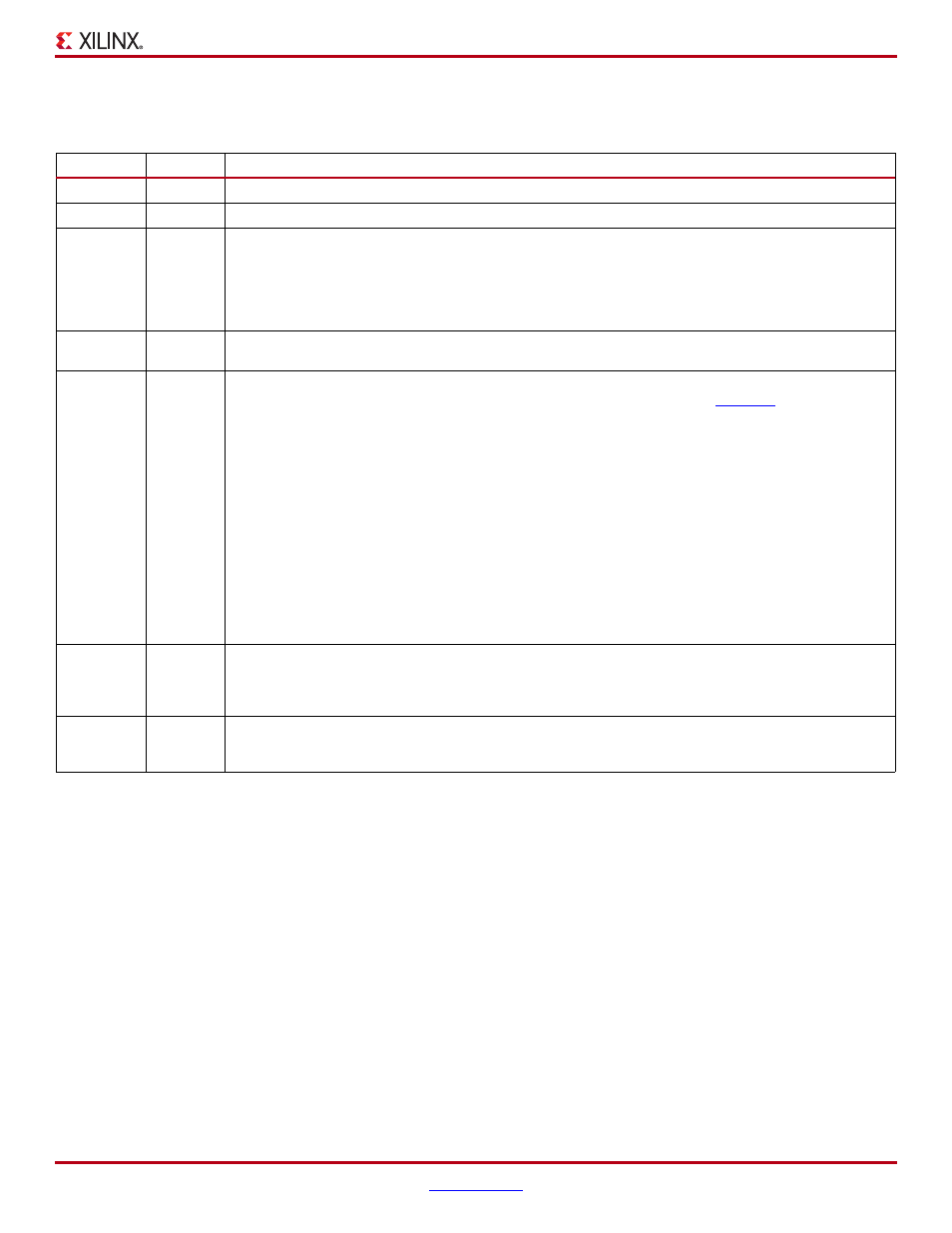

The following table shows the revision history for this document.

Date

Version

Revision

04/02/07

1.0

Initial Xilinx release.

05/25/07

1.0.1

Minor edits.

06/18/07

1.2

Updated for v1.29 production speed files. Noted banking rules in

. Added

DIFF_HSTL_I and DIFF_HSTL_III to

, and

. Updated TMDS DC characteristics

. Updated I/O Test Method values in

. Added Simultaneously Switching Output limits in

. Updated DSP48A timing symbols, descriptions, and values in

. Added power-on timing in

. Added CCLK specifications for Commercial in

through

Table 48

. Updated Slave Parallel

timing in

Table 51

. Updated JTAG specifications in

07/16/07

2.0

Added Low-power options and updated typical values for quiescent current in

. Updated DSP48A

and

06/02/08

2.1

Improved V

CCAUXT

and V

CCO2T

POR minimum in

and updated V

CCO

POR levels in

V

IN

to Recommended Operating Conditions in

and added reference to

, “Eliminating I/O

Coupling Effects when Interfacing Large-Swing Single-Ended Signals to User I/O Pins.” Reduced typical

I

CCINTQ

and I

CCAUXQ

quiescent current values by 20%-44% in

. Increased V

IL

max to 0.4V for

LVCMOS12/15/18 and improved V

IH

. Changed V

OL

max to 0.4V and

V

OH

min to V

CCO

–0.4V for LVCMOS15/18 in

. Added reference to V

CCAUX

in

. Removed DNA_RETENTION limit of 10 years in

since number of

Read cycles is the only unique limit. Updated speed files to v1.31 in

and elsewhere. Updated IOB

Setup and Hold times with device-specific values in

. Added reference to Sample Window in

. Updated IOB Propagation times with device-specific values in

. Improved SSTL_18_II

SSO value in

. Improved F

BUFG

for -4 to 334 MHz in

Table 32

. Added references to 375 MHz

performance via SCD 4103 in

Table 32

,

,

. Added explanatory footnotes to

tables. Simplified DSP48A F

MAX

to value with all registers used in

. Improved

FBUFG in

Table 32

for -4 speed grade. Updated CCLK output maximum period in

to match

minimum frequency in

Replaced BPI with SPI specification descriptions in

Table 52

. Corrected BPI

and

from falling edge to rising edge. Added references to Spartan-3 Generation User

Guides. Updated links.

03/11/09

2.2

Changed typical quiescent current temperature from ambient to quiescent. Updated selected I/O standard

DC characteristics. Removed PCIX IOSTANDARD due to limited PCIX interface support. Added T

IOPI

and

T

IOPID

to

. Updated BPI configuration waveforms in

and updated

. Removed

references to SCD 4103.

10/04/10

3.0

Added I

IK

to

. Updated description for V

IN

in

including adding note 4. Also, added note 2 to I

L

to note potential leakage between pins of a differential pair. Added note 6 to

. Updated

notes 5 and 6 in

. Corrected symbols for T

SUSPEND_GTS

and T

SUSPEND_GWE

.