Output timing adjustments, From, Table 25 – Xilinx DS610 User Manual

Page 29

Spartan-3A DSP FPGA Family: DC and Switching Characteristics

DS610 (v3.0) October 4, 2010

Product Specification

29

Output Timing Adjustments

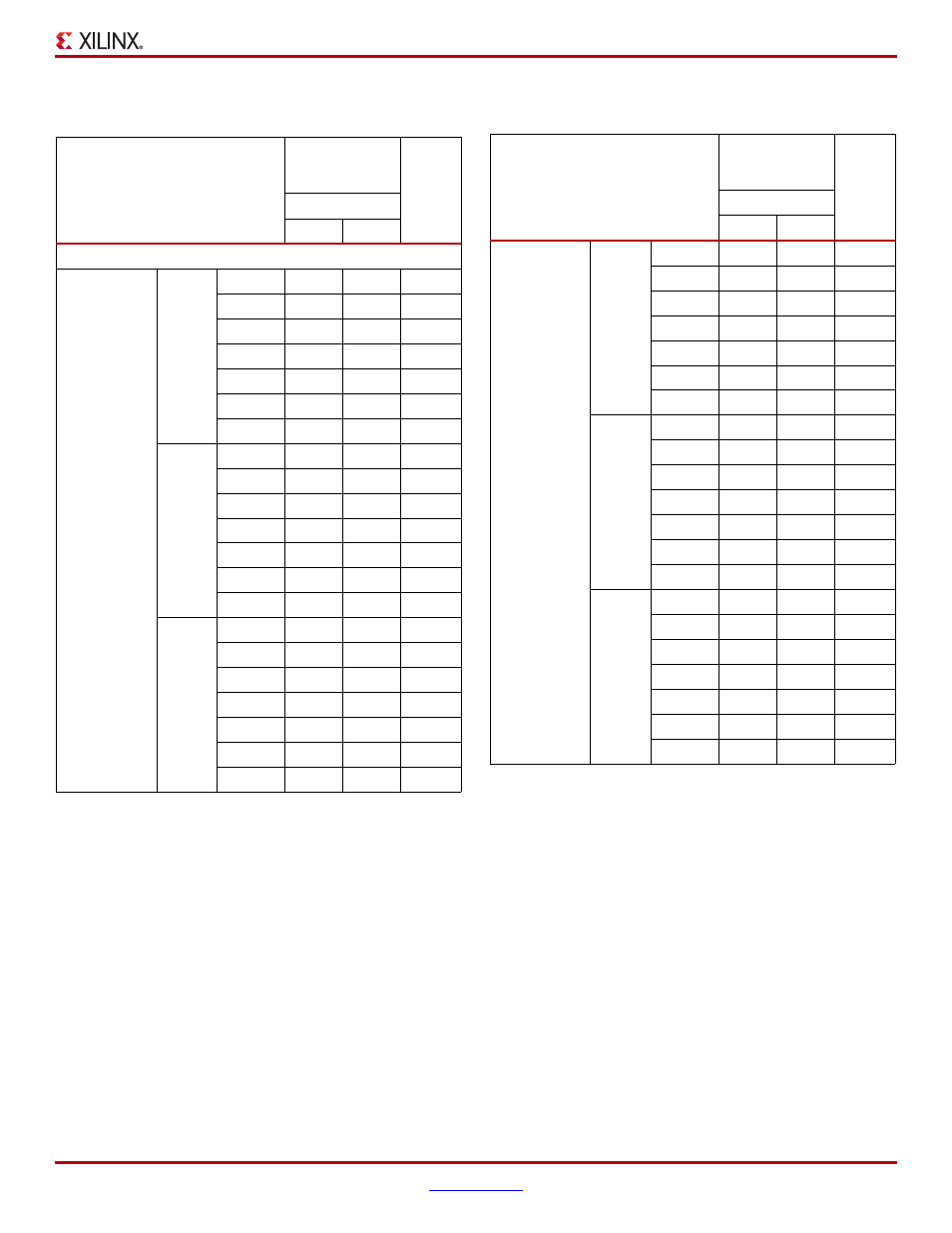

Table 25:

Output Timing Adjustments for IOB

Convert Output Time from

LVCMOS25 with 12mA Drive

and Fast Slew Rate to the

Following Signal Standard

(IOSTANDARD)

Add the

Adjustment

Below

Units

Speed Grade

-5

-4

Single-Ended Standards

LVTTL

Slow

2 mA

5.58

5.58

ns

4 mA

3.16

3.16

ns

6 mA

3.17

3.17

ns

8 mA

2.09

2.09

ns

12 mA

1.62

1.62

ns

16 mA

1.24

1.24

ns

24 mA

2.74

2.74

ns

Fast

2 mA

3.03

3.03

ns

4 mA

1.71

1.71

ns

6 mA

1.71

1.71

ns

8 mA

0.53

0.53

ns

12 mA

0.53

0.53

ns

16 mA

0.59

0.59

ns

24 mA

0.60

0.60

ns

QuietIO

2 mA

27.67

27.67

ns

4 mA

27.67

27.67

ns

6 mA

27.67

27.67

ns

8 mA

16.71

16.71

ns

12 mA

16.67

16.67

ns

16 mA

16.22

16.22

ns

24 mA

12.11

12.11

ns

LVCMOS33

Slow

2 mA

5.58

5.58

ns

4 mA

3.17

3.17

ns

6 mA

3.17

3.17

ns

8 mA

2.09

2.09

ns

12 mA

1.24

1.24

ns

16 mA

1.15

1.15

ns

24 mA

2.55

2.55

ns

Fast

2 mA

3.02

3.02

ns

4 mA

1.71

1.71

ns

6 mA

1.72

1.72

ns

8 mA

0.53

0.53

ns

12 mA

0.59

0.59

ns

16 mA

0.59

0.59

ns

24 mA

0.51

0.51

ns

QuietIO

2 mA

27.67

27.67

ns

4 mA

27.67

27.67

ns

6 mA

27.67

27.67

ns

8 mA

16.71

16.71

ns

12 mA

16.29

16.29

ns

16 mA

16.18

16.18

ns

24 mA

12.11

12.11

ns

Table 25:

Output Timing Adjustments for IOB

(Cont’d)

Convert Output Time from

LVCMOS25 with 12mA Drive

and Fast Slew Rate to the

Following Signal Standard

(IOSTANDARD)

Add the

Adjustment

Below

Units

Speed Grade

-5

-4