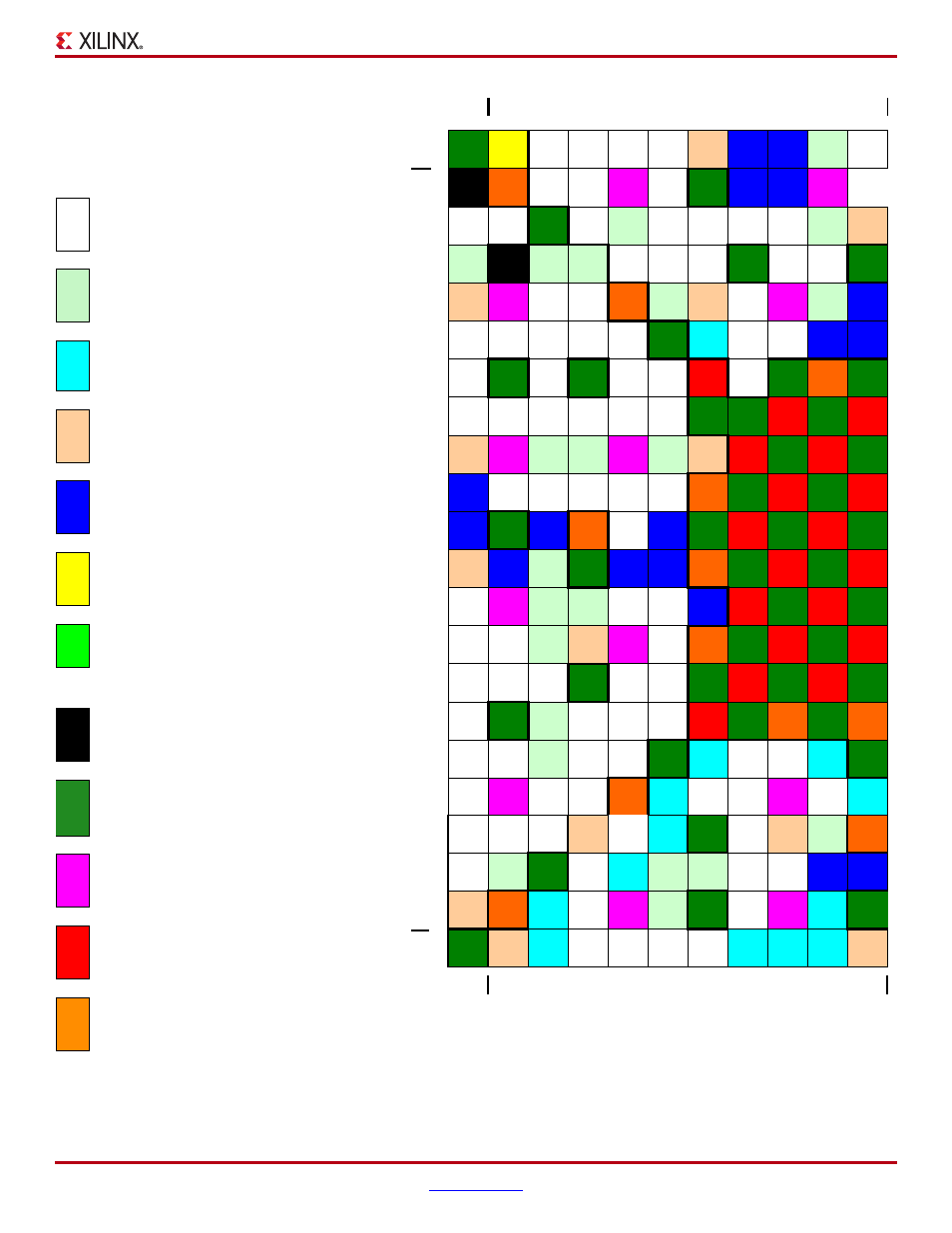

Cs484 footprint, Spartan-3a dsp fpga family: pinout descriptions, Left half of package (top view) – Xilinx DS610 User Manual

Page 73: 156 i/o, 41 input, 51 dual, 28 vref, 32 clk, 2config, S. 2

Spartan-3A DSP FPGA Family: Pinout Descriptions

DS610 (v3.0) October 4, 2010

Product Specification

73

CS484 Footprint

Left Half of Package

(Top View)

156

I/O:

Unrestricted,

general-purpose user I/O.

41

INPUT:

Unrestricted,

general-purpose input pin.

51

DUAL:

Configuration

pins, then possible user

I/O.

28

VREF:

User I/O or input

voltage reference for bank.

32

CLK:

User I/O, input, or

clock buffer input.

2

CONFIG:

Dedicated

configuration pin

s.

2

SUSPEND: Dedicated

SUSPEND and

dual-purpose AWAKE

Power Managem

ent pins.

4

JTAG:

Dedicated JTAG

port pins.

84

GND:

Ground.

24

VCCO:

Output voltage

supply for bank.

36

VCCINT:

Internal core

supply voltage (+1.2V).

24

VCCAUX:

Auxiliary

supply voltage

Figure 15: CS484 Package Footprint (Top View–Left Half)

1

2

3

4

5

6

7

8

9

10

11

A

GND

PROG_

B

I/O

L30N_0

I/O

L28N_0

I/O

L25N_0

I/O

L25P_0

I/O

L24N_0

VREF_0

I/O

L20P_0

GCLK10

I/O

L18P_0

GCLK6

INPUT

I/O

L15N_0

B

TMS

VCCAUX

I/O

L30P_0

I/O

L28P_0

VCCO_0

I/O

L24P_0

GND

I/O

L20N_0

GCLK11

I/O

L18N_0

GCLK7

VCCO_0

I/O

L15P_0

C

I/O

L02N_3

I/O

L02P_3

GND

I/O

L29N_0

INPUT

I/O

L21P_0

I/O

L26P_0

I/O

L22P_0

I/O

L16P_0

INPUT

INPUT

0

VREF_0

D

INPUT

L04P_3

TDI

INPUT

L08P_3

INPUT

L08N_3

I/O

L29P_0

I/O

L21N_0

I/O

L26N_0

GND

I/O

L22N_0

I/O

L16N_0

GND

E

INPUT

L04N_3

VREF_3

VCCO_3

I/O

L09P_3

I/O

L09N_3

VCCAUX

INPUT

I/O

L31P_0

VREF_0

I/O

L27N_0

VCCO_0

INPUT

I/O

L19N_0

GCLK9

F

I/O

L06N_3

I/O

L06P_3

I/O

L01P_3

I/O

L03P_3

I/O

L03N_3

GND

I/O

L31N_0

PUDC_B

I/O

L27P_0

I/O

L23N_0

I/O

L19P_0

GCLK8

I/O

L17N_0

GCLK5

G

I/O

L11P_3

GND

I/O

L01N_3

GND

I/O

L07P_3

I/O

L07N_3

VCCINT

I/O

L23P_0

GND

VCCAUX

GND

H

I/O

L11N_3

I/O

L14P_3

I/O

L05P_3

I/O

L05N_3

I/O

L10P_3

I/O

L10N_3

GND

GND

VCCINT

GND

VCCINT

J

I/O

L14N_3

VREF_3

VCCO_3

INPUT

L16P_3

INPUT

L16N_3

VCCO_3

INPUT

L12P_3

INPUT

L12N_3

VREF_3

VCCINT

GND

VCCINT

GND

K

I/O

L19P_3

LHCLK2

I/O

L17P_3

I/O

L17N_3

I/O

L13P_3

I/O

L13N_3

I/O

L15P_3

VCCAUX

GND

VCCINT

GND

VCCINT

L

I/O

L19N_3

IRDY2

LHCLK3

GND

I/O

L20P_3

LHCLK4

VCCAUX

I/O

L15N_3

I/O

L18P_3

LHCLK0

GND

VCCINT

GND

VCCINT

GND

M

I/O

L22P_3

VREF_3

I/O

L20N_3

LHCLK5

INPUT

L23P_3

GND

I/O

L18N_3

LHCLK1

I/O

L21P_3

TRDY2

LHCLK6

VCCAUX

GND

VCCINT

GND

VCCINT

N

I/O

L22N_3

VCCO_3

INPUT

L31P_3

INPUT

L23N_3

I/O

L24N_3

I/O

L24P_3

I/O

L21N_3

LHCLK7

VCCINT

GND

VCCINT

GND

P

I/O

L25P_3

I/O

L25N_3

INPUT

L31N_3

I/O

L32P_3

VREF_3

VCCO_3

I/O

L26P_3

VCCAUX

GND

VCCINT

GND

VCCINT

R

I/O

L28N_3

I/O

L28P_3

I/O

L34P_3

GND

I/O

L32N_3

I/O

L26N_3

GND

VCCINT

GND

VCCINT

GND

T

I/O

L30P_3

GND

INPUT

L27P_3

I/O

L34N_3

I/O

L29N_3

I/O

L29P_3

VCCINT

GND

VCCAUX

GND

VCCAUX

U

I/O

L30N_3

I/O

L33P_3

INPUT

L27N_3

I/O

L38P_3

I/O

L38N_3

GND

I/O

L02N_2

CSO_B

I/O

L11N_2

I/O

L10N_2

I/O

L14N_2

D4

GND

V

I/O

L33N_3

VCCO_3

I/O

L36N_3

I/O

L36P_3

VCCAUX

I/O

L02P_2

M2

I/O

L11P_2

I/O

L06N_2

VCCO_2

I/O

L10P_2

I/O

L14P_2

D5

Ba

nk

3

Bank 0

W

I/O

L35N_3

I/O

L37N_3

I/O

L37P_3

INPUT

2

VREF_2

I/O

L03P_2

I/O

L07N_2

VS2

GND

I/O

L06P_2

INPUT

2

VREF_2

INPUT

VCCAUX

Y

I/O

L35P_3

INPUT

L39P_3

GND

I/O

L03N_2

I/O

L07P_2

RDWR_B

INPUT

INPUT

I/O

L13P_2

I/O

L13N_2

I/O

L15N_2

GCLK13

I/O

L15P_2

GCLK12

A

A

INPUT

L39N_3

VREF_3

VCCAUX

I/O

L01P_2

M1

I/O

L04N_2

VCCO_2

INPUT

GND

I/O

L08N_2

VCCO_2

I/O

L12N_2

D6

GND

A

B

GND

INPUT

2

VREF_2

I/O

L01N_2

M0

I/O

L04P_2

I/O

L05P_2

I/O

L05N_2

I/O

L08P_2

I/O

L09P_2

VS1

I/O

L09N_2

VS0

I/O

L12P_2

D7

INPUT

2

VREF_2

Bank 2