Timer area – Omron HOME SECURITY SYSTEM - MOTION SENSOR FQM1-MMA21 User Manual

Page 328

305

I/O Memory

Appendix B

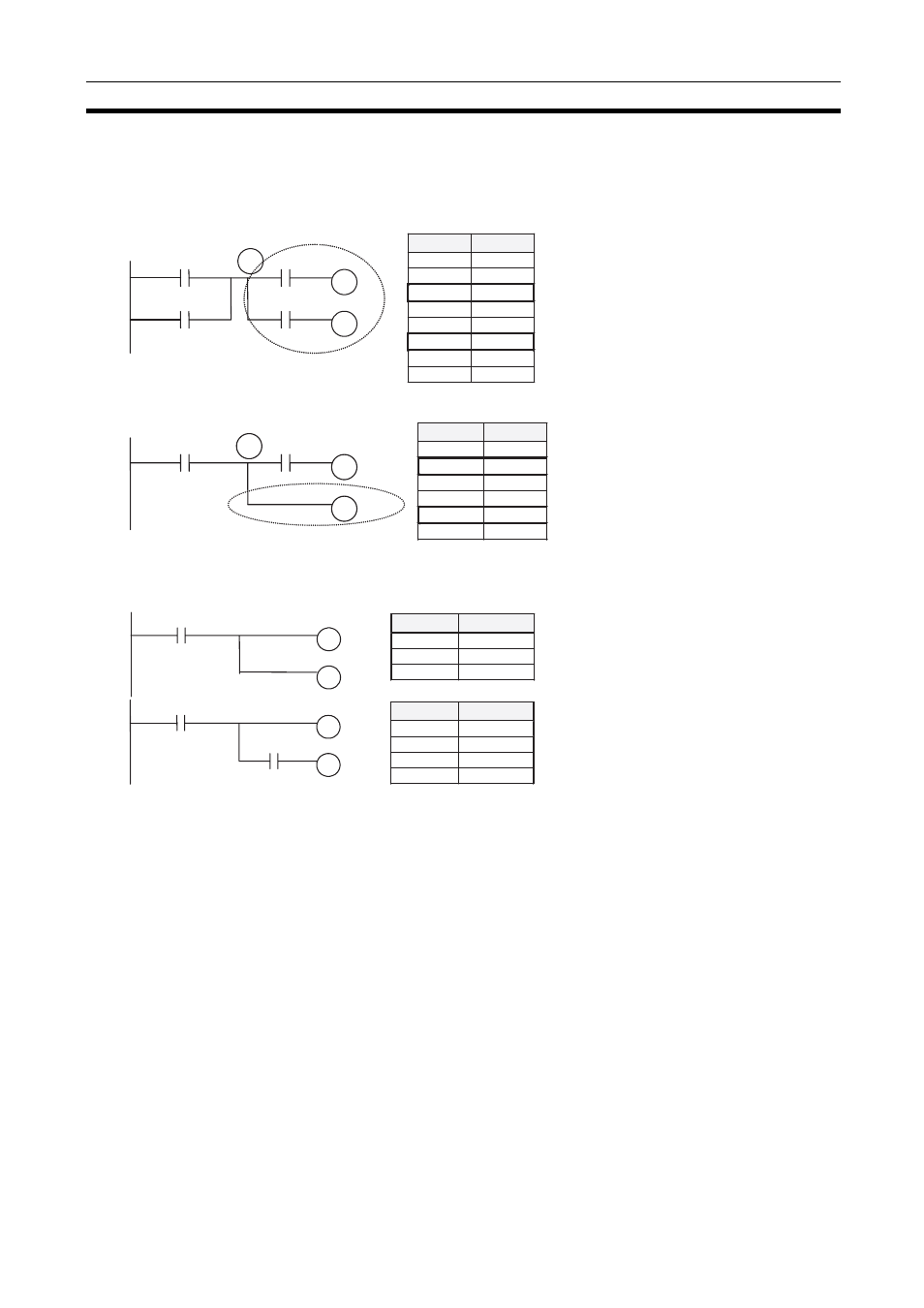

• Each TR bit can be used only once in one program section.

• The status of TR bits cannot be changed from the CX-Programmer.

TB bits are used in the following cases.

• When there are two outputs with different LD instructions after the last branch point:

• When there is no LD instruction on the lower rung after a branch point:

Note In the following cases, there are either no LD instructions after the branch points, or any LD instructions

are on the bottom rung. TR bits are not required in these types of branches.

Timer Area

The 256 timer numbers (T0000 to T0255) are shared by the TIM, TIMH(015), and TMHH(540) instructions.

Timer Completion Flags and present values (PVs) for these instructions are accessed with the timer numbers.

When a timer number is used in an operand that requires bit data (e.g., in LD, AND, or OR instructions), the

timer number accesses the Completion Flag of the timer. When a timer number is used in an operand that

requires word data (e.g., in MOV(021) or CMP(020) instructions), the timer number accesses the PV of the

timer. Timer Completion Flags can be used as often as necessary as normally open and normally closed con-

ditions and the values of timer PVs can be read as normal word data.

Timer Completion Flags can be force-set and force-reset.

Timer PVs cannot be force-set or force-reset, although the PVs can be refreshed indirectly by force-setting/

resetting the Completion Flag.

There are no restrictions in the order of using timer numbers or in the number of NC or NO conditions that can

be programmed. Timer PVs can be read as word data and used in programming.

Note It is not recommended to use the same timer number in two timer instructions because the timers will not

operate correctly if they are timing simultaneously. (If two or more timer instructions use the same timer

number, an error will be generated during the program check, but the timers will operate as long as the

instructions are not executed in the same cycle.)

TR0

0000.00

0002.05

0000.01

0000.02

0000.04

0002.03

LD

0000.00

OR

0000.01

OUT

TR 0

AND

0000.02

OUT

0002.03

LD

TR 0

AND

0000.04

OUT

0002.05

Instruction

Operand

TR0

0000.00

0000.01

0002.02

0002.03

LD

0000.00

OUT

TR 0

AND

OUT

0002.02

LD

TR 0

OUT

0002.03

0000.0

1

Instruction

Operand

0000.00

0002.01

0002.02

0000.00

0002.01

0002.03

0000.02

LD

0000.00

OUT

0002.01

OUT

0002.02

LD

0000.00

OUT

0002.01

AND

0000.02

OUT

0002.03

Instruction

Operand

Instruction

Operand