NEC PD750008 User Manual

Page 50

3 0

µPD750008 USER'S MANUAL

(a) Specific address bit direct addressing (fmem.bit)

In this addressing mode, peripheral equipment that frequently performs bit manipulations involving,

for example, I/O ports and interrupt flags, can be processed at all times regardless of memory bank

setting. Accordingly, the data memory addresses that allow this addressing mode to be used are FF0H

to FFFH where I/O ports are mapped, and FB0H to FBFH where interrupt-related hardware is mapped.

Hardware mapped to these data memory areas can freely perform bit manipulations in the direct

addressing mode at any time regardless of MBS and MBE setting.

Examples 1. Value input to P02 is inverted, and the result is output on P33.

MOV1

CY, PORT0.2

NOT1

CY

MOV1

PORT3.3, CY

2. The timer 0 interrupt request flag (IRQT0) is tested. The request flag, if set, is cleared,

and P63 is reset.

SKTCLR

IRQT0

; IRQT0 = 1?

BR

NO

; NO

CLR1

PORT6.3

; YES

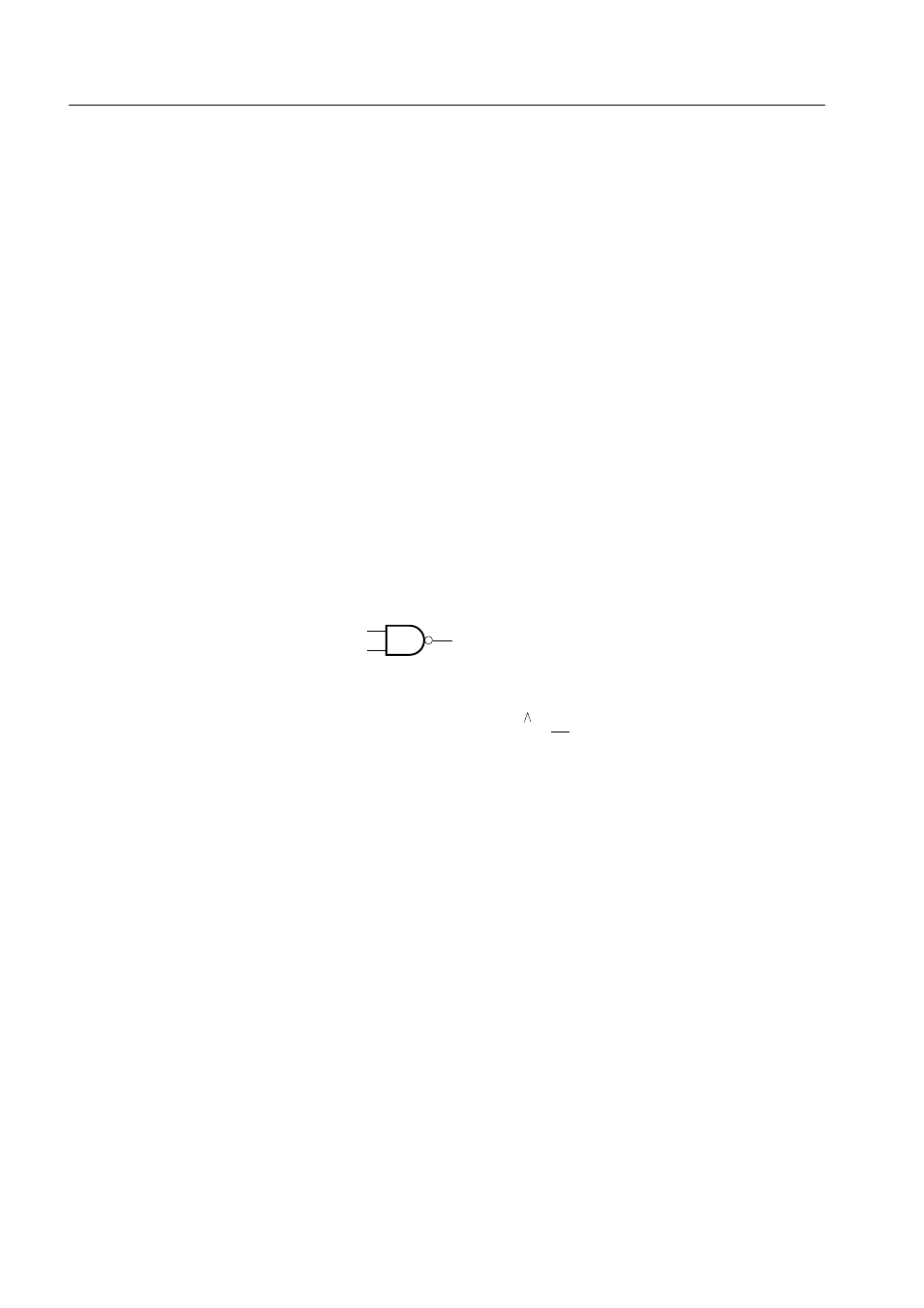

3. If both P30 and P41 are set to 1, P53 is reset.

MOV1

CY, PORT3.0

; CY <– P30

AND1

CY, PORT4.1

; CY P41

NOT1

CY

; CY <– CY

MOV1

PORT5.3, CY

; P53 <– CY

P53

P30

P41