NEC PD750008 User Manual

Page 159

139

CHAPTER 5 PERIPHERAL HARDWARE FUNCTIONS

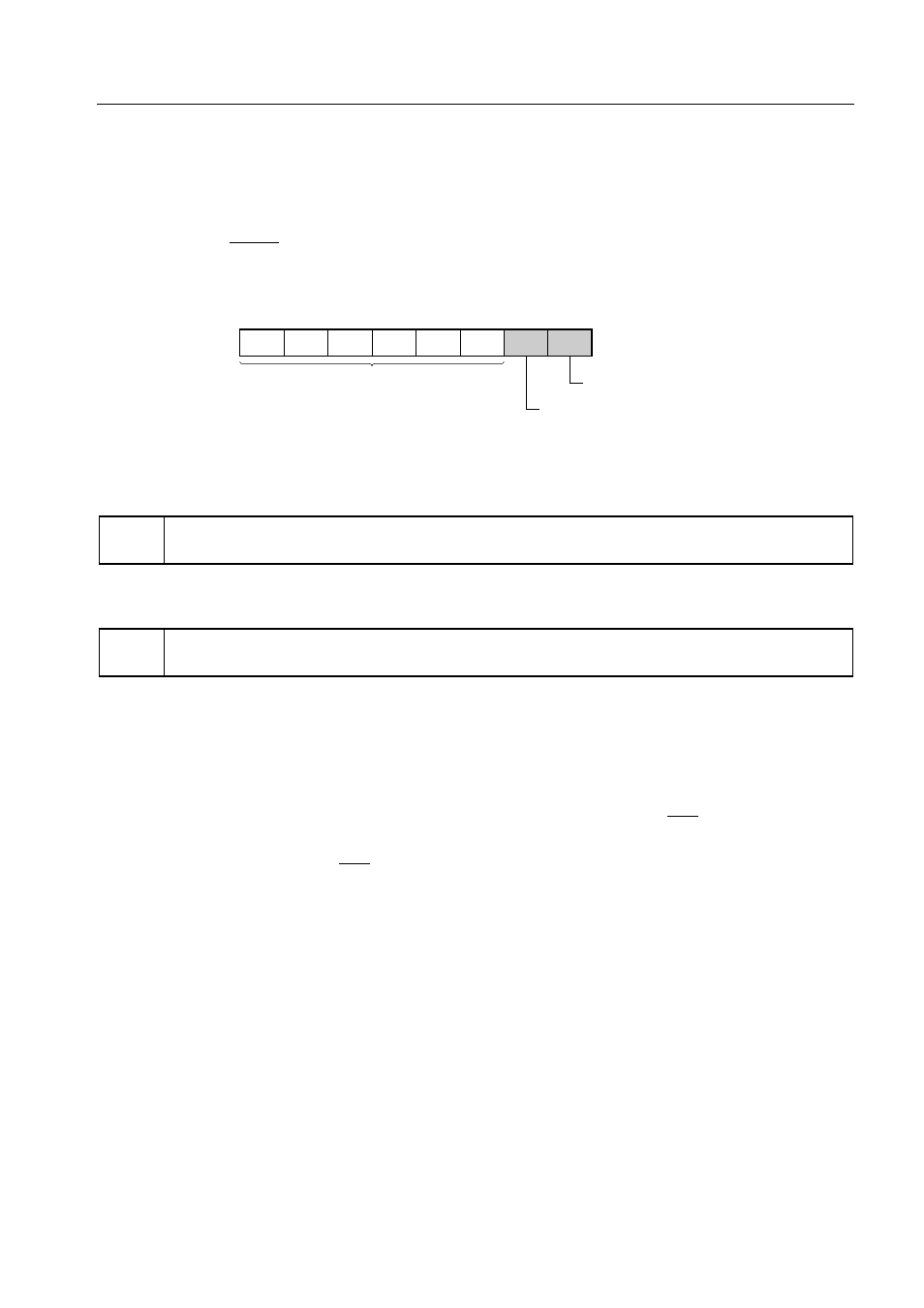

(b) Serial bus interface control register (SBIC)

To use the three-wire serial I/O mode, set SBIC as shown below. (For details on SBIC format, see

(2) in Section 5.6.3.)

SBIC is manipulated using a bit memory manipulation instruction.

When the RESET signal is input, SBIC is set to 00H.

In the figure below, hatched portions indicate the bits used in the three-wire serial I/O mode.

Remark (W): Write only

Command trigger bit (W)

CMDT

Control bit for command signal (CMD) trigger output. By setting CMDT = 1, the SO latch is

cleared. Then the CMDT bit is automatically cleared.

Bus release trigger bit (W)

RELT

Control bit for bus release signal (REL) trigger output.

By setting RELT = 1, the SO latch is set to 1. Then the RELT bit automatically cleared to 0.

Caution Never use bits other than RELT and CMDT in the three-wire serial I/O mode.

(2) Communication operation

The three-wire serial I/O mode transfers data, with eight bits as one block. Data is transferred bit by bit

in phase with the serial clock.

The shift register performs shift operation on the falling edge of the serial clock (SCK). Send data is latched

on the SO latch, and is output on the SO pin. Receive data applied to the SI pin is latched in the shift

register on the rising edge of SCK.

When eight bits have been transferred, shift register operation automatically terminates setting the

interrupt request flag (IRQCSI).

BSYE ACKD ACKE ACKT CMDD RELD CMDT RELT

FE2H

SBIC

7

6

5

4

3

2

1

0

Address

Bus release trigger bit (W)

Command trigger bit (W)

Do not use these bits in the

three-wire serial I/O mode.