NEC PD750008 User Manual

Page 108

88

µPD750008 USER'S MANUAL

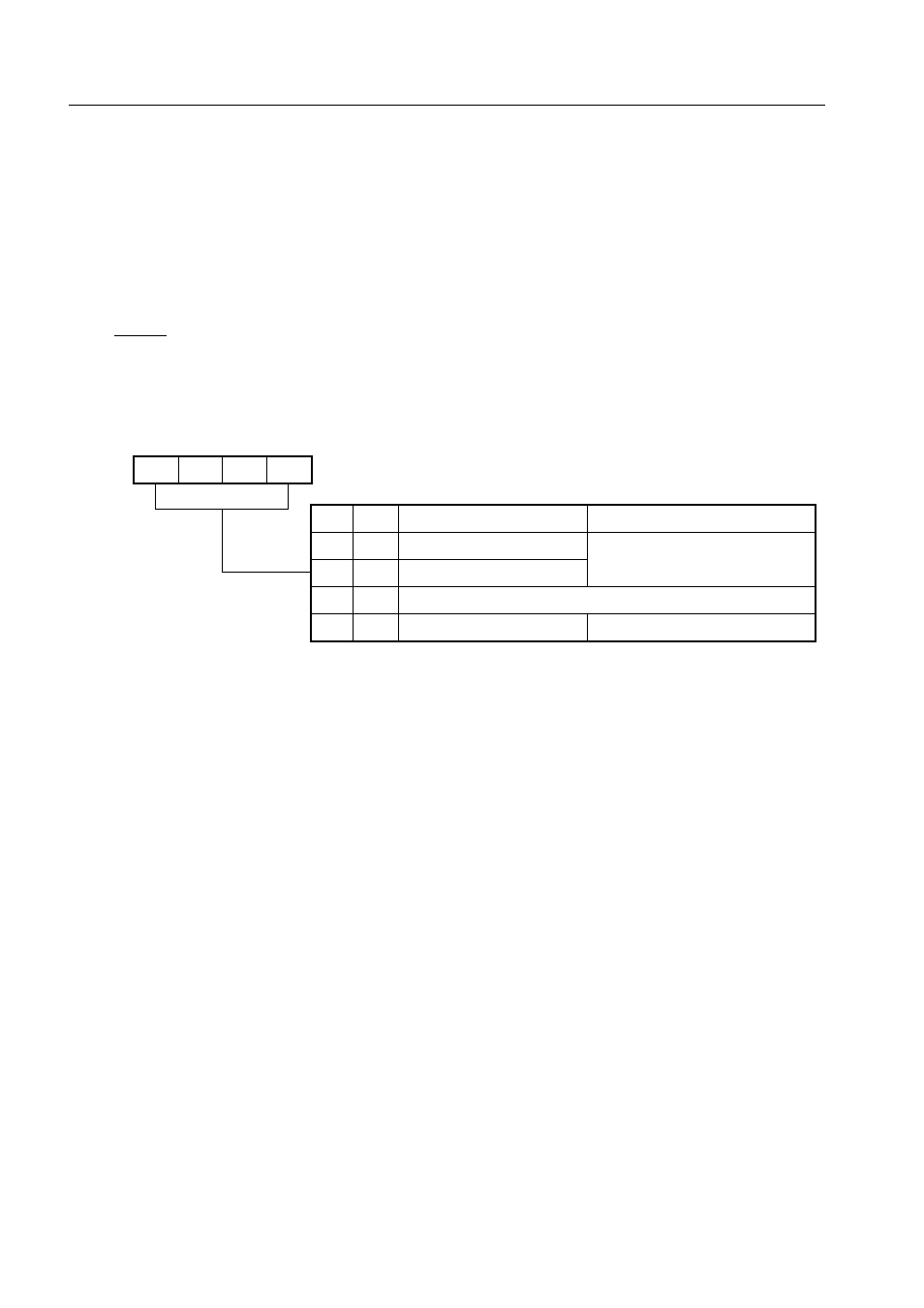

(2) System clock control register (SCC)

The SCC is a 4-bit register for selecting CPU clock

F

with the least significant bit and for controlling the

termination of main system clock generation with the most significant bit (see Figure 5-13).

Bits 0 and 3 of the SCC are located at the same data memory address, but both bits cannot be changed

at the same time. Accordingly, bits 0 and 3 of the SCC are set using bit manipulation instructions. Bits

0 and 3 of the SCC can be manipulated regardless of MBE setting.

Main system clock generation can be terminated by setting bit 3 of the SCC only when the subsystem

clock is used for operation. The STOP instruction must be used to terminate main system clock generation.

A RESET signal clears the SCC to 0.

Figure 5-13. Format of the System Clock Control Register

Cautions 1. A time period of up to 1/f

XT

is needed to change the system clock. This means

that to terminate main system clock generation, bit 3 of the SCC must be set to 1

when the machine cycles indicated in Table 5-4 or more have elapsed after the

clock is switched from the main system clock to the subsystem clock.

2. When the main system clock is used for operation, setting bit 3 of the SCC to

stop clock generation does not enter the normal STOP mode.

3. When the PCC is set to 0001B (

F

F

F

F

F

= f

X

/16), do not set SCC.0 to 1. Before switch-

ing the main system clock to the subsystem clock, be sure to manipulate the

PCC so other than 0001B is set. When the system operates on the subsystem

clock, the PCC must also be other than 0001B.

4. When SCC.3 is set to 1, the X1 input pin is connected to V

SS

(ground electric

potential) to prevent leakage in the crystal oscillator. When an external clock is

used as the main system clock, never set SCC.3 to 1.

Address

FB7H

SCC3

—

—

SCC0

Symbol

SCC

CPU clock frequency

Main system clock

Main system clock operation

Subsystem clock

Can oscillate

Subsystem clock

0

0

1

0

0

1

1

1

Oscillation stopped

SCC0

SCC3

Not to be set

3

2

1

0