768 khz – NEC PD750008 User Manual

Page 127

107

CHAPTER 5 PERIPHERAL HARDWARE FUNCTIONS

Example Time is set using the main system clock (4.19 MHz), and buzzer output is enabled:

CLR1

MBE

MOV

XA, #84H

MOV

WM, XA

; Sets WM

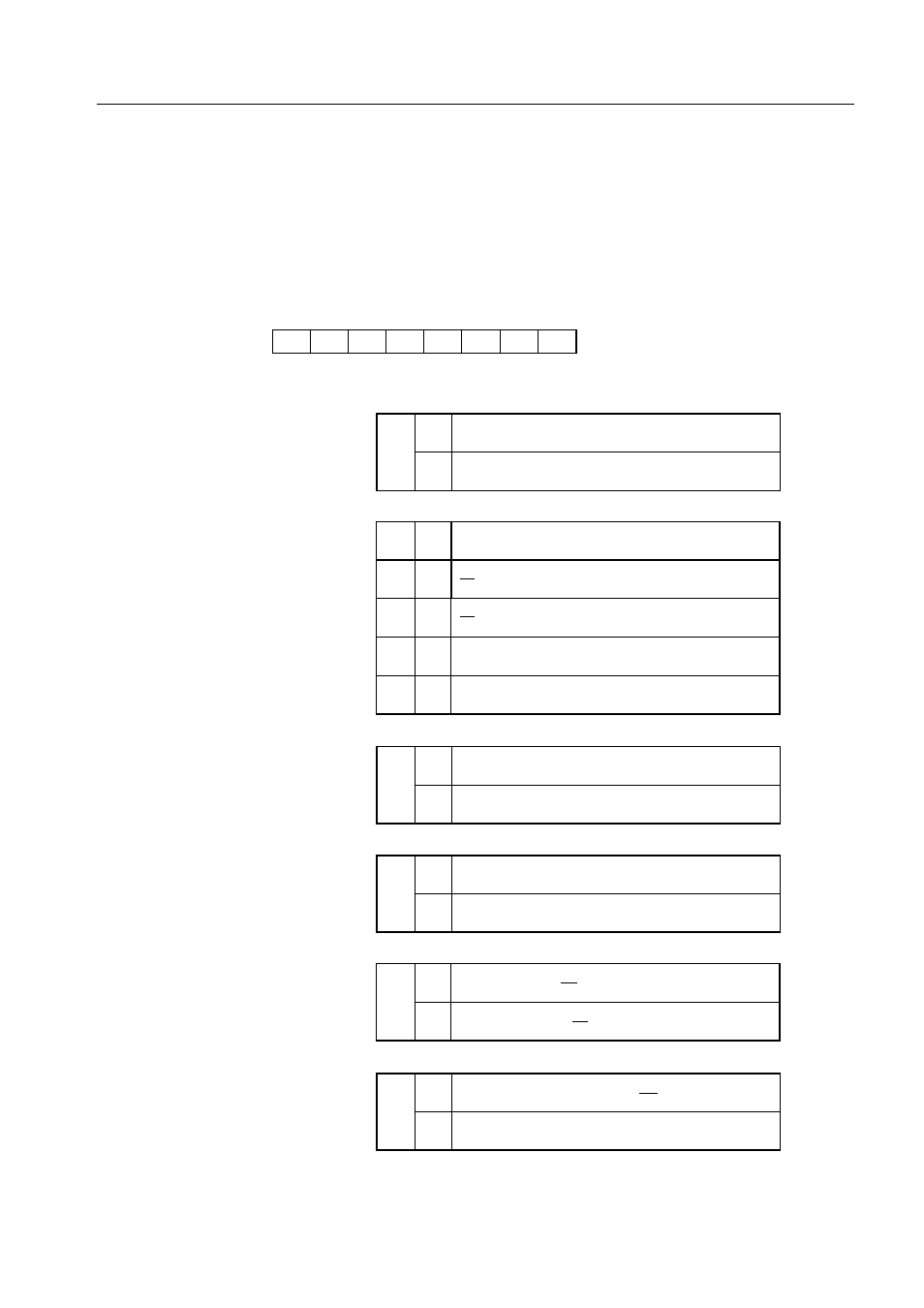

Figure 5-27. Clock Mode Register Format

Remark ( ) for f

W

= 32.768 kHz

Address

F98H

Symbol

WM

0

WM0

1

WM1

2

WM2

3

WM3

4

WM4

5

WM5

6

0

7

WM7

WM0

0

1

Selects divided system clock output:

Selects subsystem clock: f

XT

Count clock (f

W

) selection bit

WM1

0

1

Normal clock mode ( : sets IRQW at 0.5 seconds)

Advanced clock mode ( : sets IRQW at 3.91 ms)

Operation mode selection bit

WM2

0

1

Disables clock operation (clears the frequency dividing circuit)

Enables clock operation

Clock operation enable/disable bit

WM3

0

1

Input to the XT1 pin is low level

Input to the XT1 pin is high level

XT1 pin input level (bit test only)

WM5

WM4

0

BUZ output frequency

(2.048 kHz)

BUZ output frequency selection bit

WM7

0

1

Disables BUZ output

Enables BUZ output

BUZ output enable/disable bit

1

0

(4.096 kHz)

Not to be set

1

f

W

(32.768 kHz)

0

0

1

1

f

W

2

14

f

X

128

f

W

2

7

f

W

2

4

f

W

2

3