Interrupt sequence – NEC PD750008 User Manual

Page 215

195

CHAPTER 6 INTERRUPT AND TEST FUNCTIONS

6.4 INTERRUPT SEQUENCE

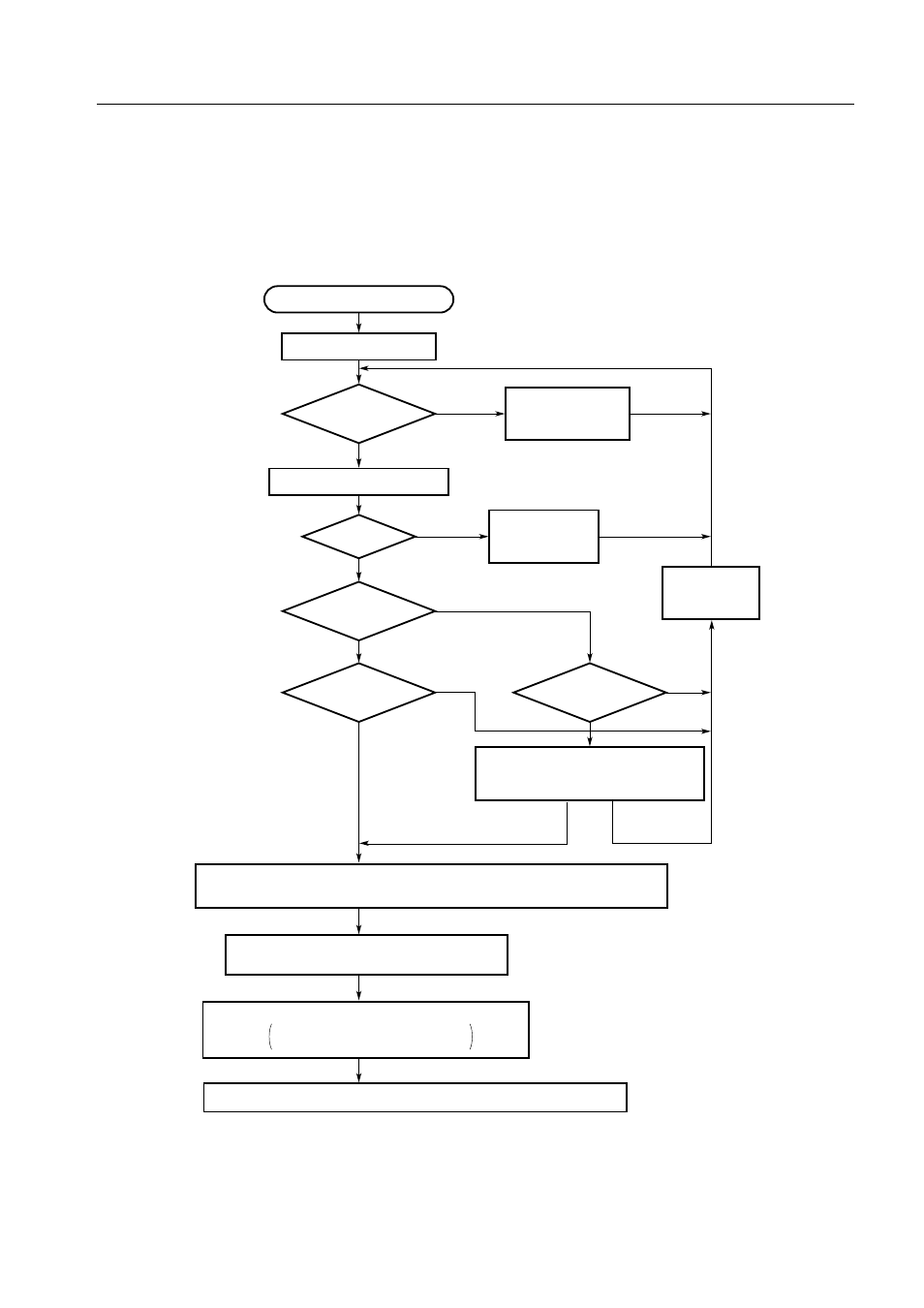

When an interrupt occurs, it is processed using the procedure shown in Figure 6-7.

Figure 6-7. Interrupt Sequence

Notes 1. IST0 and IST1 are the interrupt status flags (bits 3 and 2 of the PSW). (See Table 6-3.)

2. An interrupt service program start address and MBE and RBE setting values at the

start of interrupt are stored in each vector table.

No

Yes

Yes

No

Yes

No

No

Yes

No

Yes

Interrupt (INTxxx) occurrence

IRQxxx setting

IExxx set?

Hold until IExxx is set.

Corresponding VRQn occurrence

IME = 1

Hold until IME

is set.

Is

VRQn high-order

interrupt?

Note 1

IST1, 0 = 00 or 01

Note 1

IST1, 0 = 00

If two or more VRQns occur, select

one VRQn according to Table 6-1.

Selected

VRQn

Remaining

VRQns

Save contents of PC and PSW in stack memory and set data

Note 2

in vector table

corresponding to activated VRQn to PC, RBE, and MBE.

Change contents of IST0 and IST1 from 00 to 01

or from 01 to 10.

Reset accepted IRQxxx.

See Section 6.6 when those interrupt

sources share vector address.

Jump to the start address for processing the interrupt service program.

Hold until process-

ing being executed

is finished.