Int2, Kr0-kr3, Kr4-kr7 – NEC PD750008 User Manual

Page 35: X1, x2

1 5

CHAPTER 2 PIN FUNCTIONS

INT0 has a noise eliminator. Two different sampling clocks for noise elimination can be switched. The

acceptable width of a signal depends on the CPU clock.

INT1 is an asynchronous input, and can accept a signal with some high level width regardless of what the

CPU clock is.

A RESET input clears IM0 and IM1 to 0, selecting rising edge active.

The INT1 pin can also be used to release the STOP and HALT modes, but the INT0 pin cannot.

Schmitt-triggered inputs are used for the INT0 and INT1 pins.

2.2.11 INT2: Input Pin Used Also for Port 1

This is a rising edge active, external test input pin. When INT2 is selected with the edge detection mode

register (IM2), or when the signal applied to this pin goes high, the internal test flag (IRQ2) is set.

INT2 is an asynchronous input, and can accept a signal with some high level width regardless of the

operating clock of the CPU.

A RESET signal clears IM2 to 0. In this case, the test flag (IRQ2) is set by a rising edge on the INT2 pin.

The INT2 pin can also be used to release the STOP and HALT modes. A Schmitt-triggered input is used

for this pin.

2.2.12

KR0-KR3: Input Pins Used Also for Port 6

KR4-KR7: Input Pins Used Also for Port 7

KR0 to KR7 are key interrupt input pins. An interrupt is caused when parallel falling edges are detected

on them. The interrupt format can be specified with the edge detection mode register (IM2).

A RESET signal places these pins in the port 6 and 7 input modes.

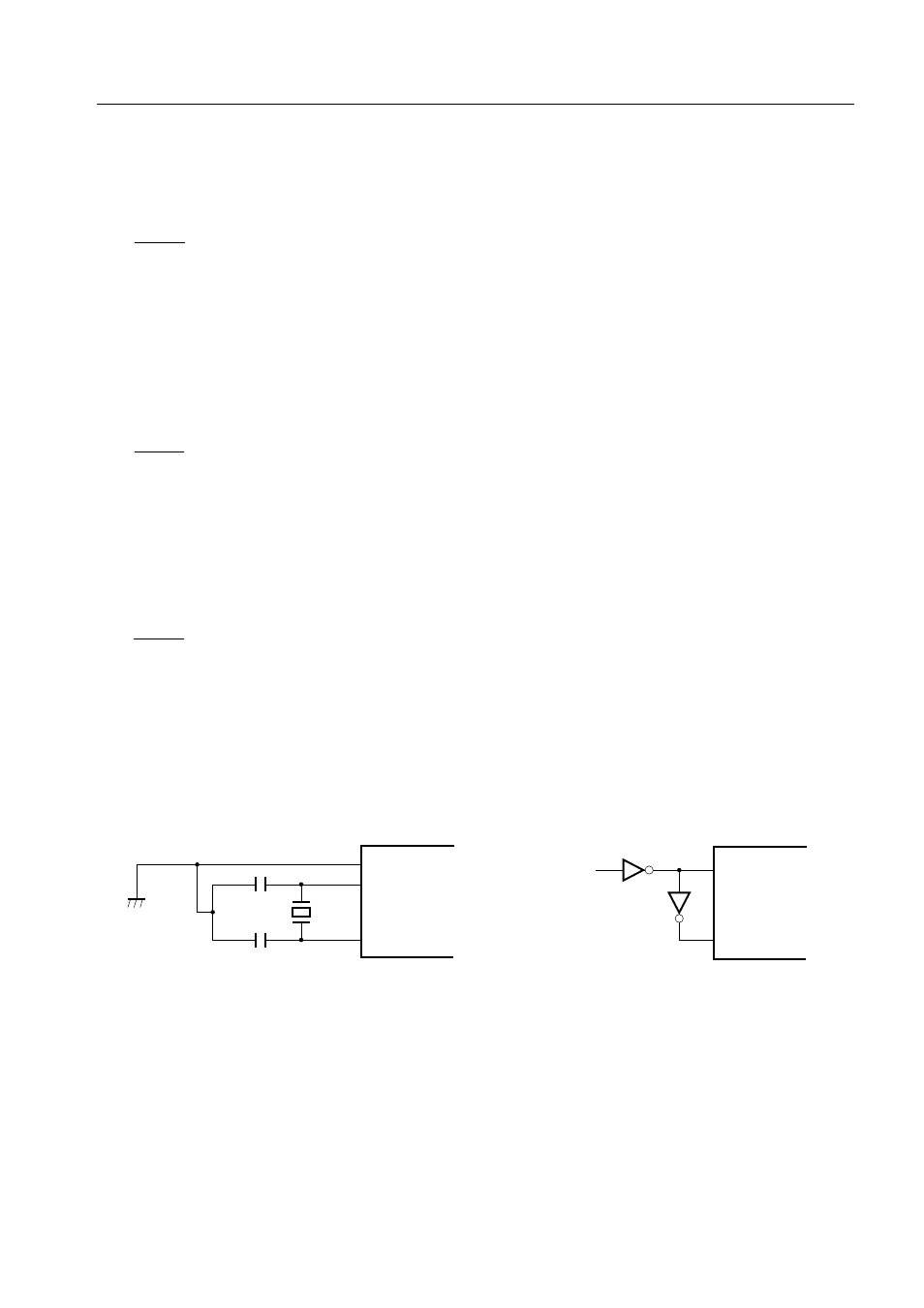

2.2.13 X1, X2

These pins are used for connection to a crystal or ceramic resonator for main system clock generation.

An external clock can also be applied.

(a) Crystal/ceramic oscillation

(b) External clock

V

SS

X1

X2

Crystal or ceramic resonator

µPD750008

(Standard frequency:

4.194304 or 6.0 MHz)

PD74HC04

X1

X2

External

clock

µPD750008

µ