NEC PD750008 User Manual

Page 320

300

µPD750008 USER'S MANUAL

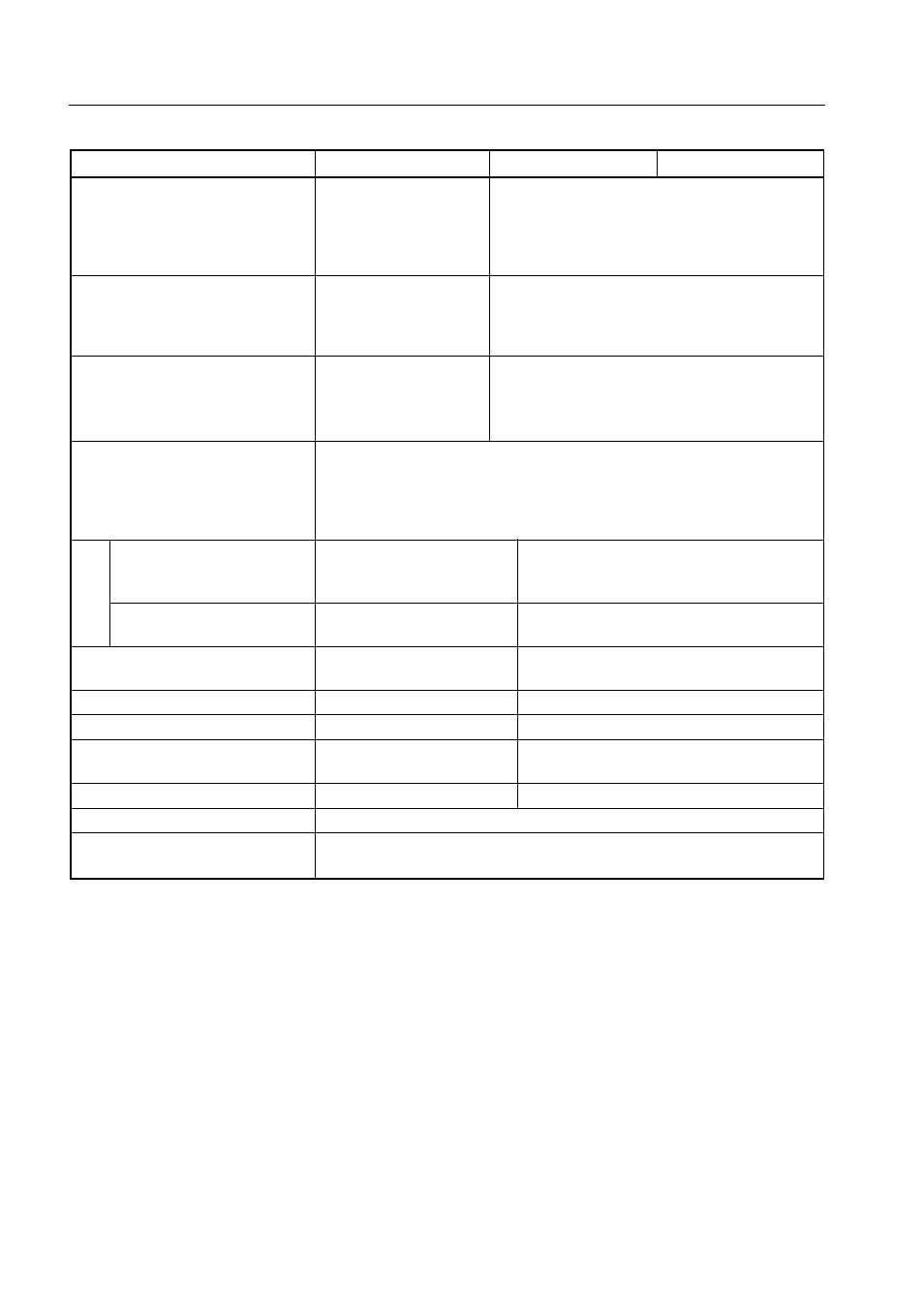

Item

(2/2)

SOS register

Serial interface

Feedback resistor cut

flag (SOS.0)

Sub-oscillator current cut

flag (SOS.1)

Register bank selection register

(RBS)

Standby release with INT0

Number of vectored interrupts

Processor clock control register

Power supply voltage

Operating ambient temperature

Package

Timer

Clock output (PCL)

BUZ output (BUZ)

4 channels

• Basic interval timer/watchdog timer: 1

• Timer/event counter: 1

• Timer/counter: 1

• Clock timer: 1

•

F

, 524, 262, 65.5 kHz

(when the main system clock operates at 4.19 MHz)

•

F

, 750, 375, 93.7 kHz

(when the main system clock operates at 6.0 MHz)

• 2, 4, 32 kHz

(when the main system clock operates at 4.19 MHz)

• 2.86, 5.72, 45.8 kHz

(when the main system clock operates at 6.0 MHz)

3 channels

• Basic interval timer: 1

• Timer/event counter: 1

• Clock timer: 1

F

, 524, 262, 65.5 kHz

(when the main system

clock operates at 4.19

MHz)

2 kHz

3 modes supported

• Three-wire serial I/O mode: First transferred bit switchable between the

LSB and MSB

• Two-wire serial I/O mode

• SBI mode

Can incorporate feedback

resistors that are specified

with the mask option.

Not provided

Not provided

Disable

External: 3, internal: 3

Available when PCC is 0,

2, or 3

V

DD

= 2.7 to 6.0 V

Incorporated

Incorporated

Provided

Enable

External: 3, internal: 4

Available when PCC is 0 to 3

V

DD

= 2.2 to 5.5 V

µPD75008 µPD750008 µPD75P0016

T

A

= –40 to +85 °C

• 42-pin plastic shrink DIP (600 mil)

• 44-pin plastic QFP (10 x 10 mm)