NEC PD750008 User Manual

Page 149

129

CHAPTER 5 PERIPHERAL HARDWARE FUNCTIONS

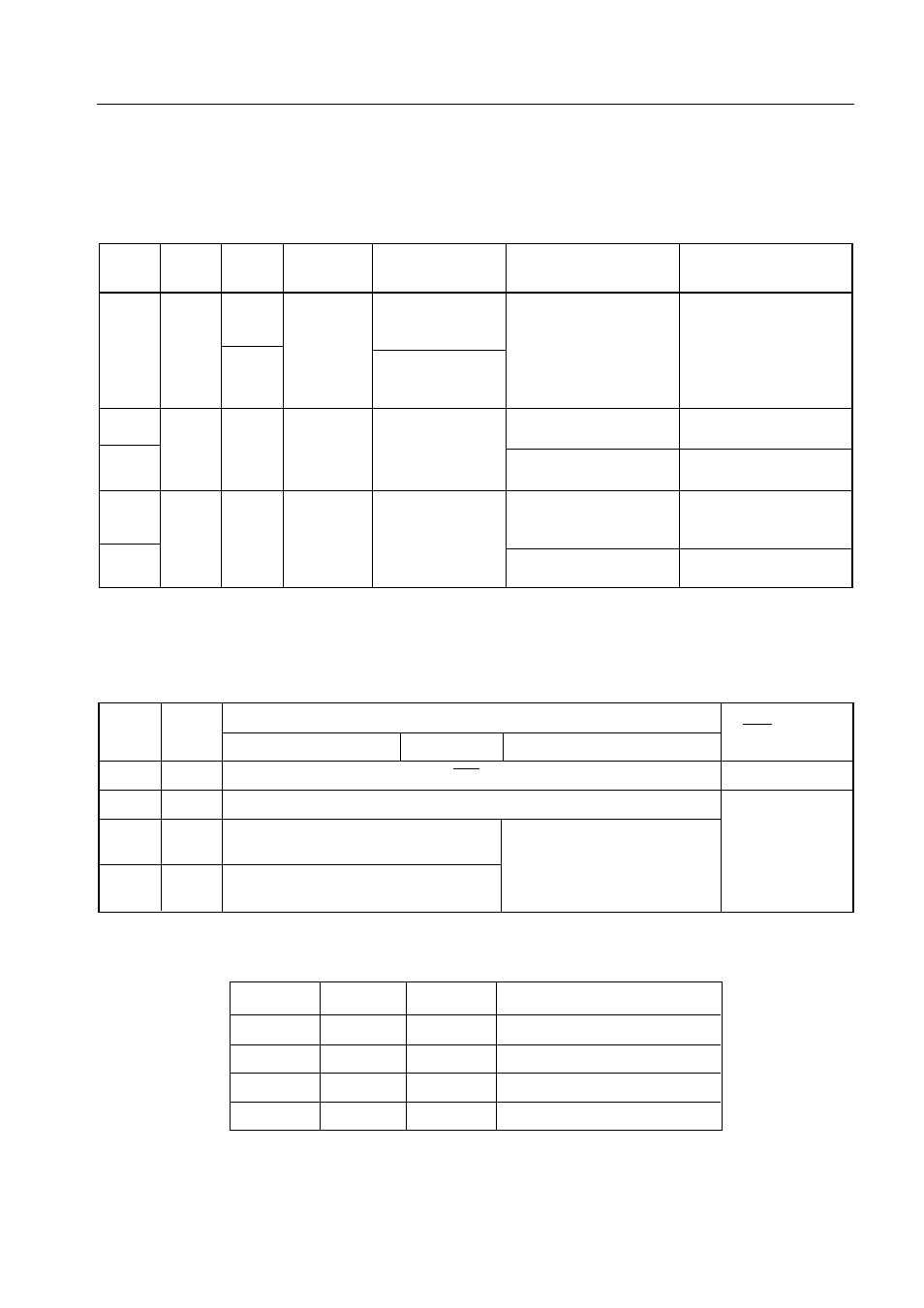

Figure 5-40. Format of Serial Operation Mode Register (CSIM) (3/4)

Serial interface operation mode selection bit (W)

CSIM4

CSIM3

CSIM2

Operation

Bit order of

SO pin

SI pin

mode

shift register

function

function

x

0

0

3-wire

SIO

7-0

<—> XA

SO/P02

SI/P03

serial

(Transfer start

(CMOS output)

(Input)

I/O mode

with MSB)

1

SIO

0-7

<—> XA

(Transfer starting

with LSB)

0

1

0

SBI mode

SIO

7-0

<—> XA

SB0/P02

P03 input

(Transfer starting

(N-ch open-drain I/O)

1

with MSB)

P02 input

SB1/P03

(N-ch open-drain I/O)

0

1

1

2-wire

SIO

7-0

<—> XA

SB0/P02

P03 input

serial

(Transfer starting

(N-ch open-drain I/O)

I/O mode

with MSB)

1

P02 input

SB1/P03

(N-ch open-drain I/O)

Remark x: Don’t care

Serial clock selection bit (W)

CSIM1

CSIM0

Serial clock

SCK pin mode

3-wire serial I/O mode

SBI mode

2-wire serial I/O mode

0

0

Input clock externally applied to SCK pin

Input

0

1

Timer/event counter output (TOUT0)

Output

1

0

f

X

/2

4

(375 kHz: at 6.00 MHz,

f

X

/2

6

(93.8 kHz: at 6.00 MHz,

262 kHz: at 4.19 MHz)

65.47 kHz: at 4.19 MHz)

1

1

f

X

/2

3

(750 kHz: at 6.00 MHz,

524 kHz: at 4.19 MHz)

Remarks 1. Each mode can be selected using CSIE, CSIM3, and CSIM2.

CSIE

CSIM3

CSIM2

Operation mode

0

x

x

Operation halt mode

1

0

x

Three-wire serial I/O mode

1

1

0

SBI mode

1

1

1

Two-wire serial I/O mode