NEC PD750008 User Manual

Page 129

109

CHAPTER 5 PERIPHERAL HARDWARE FUNCTIONS

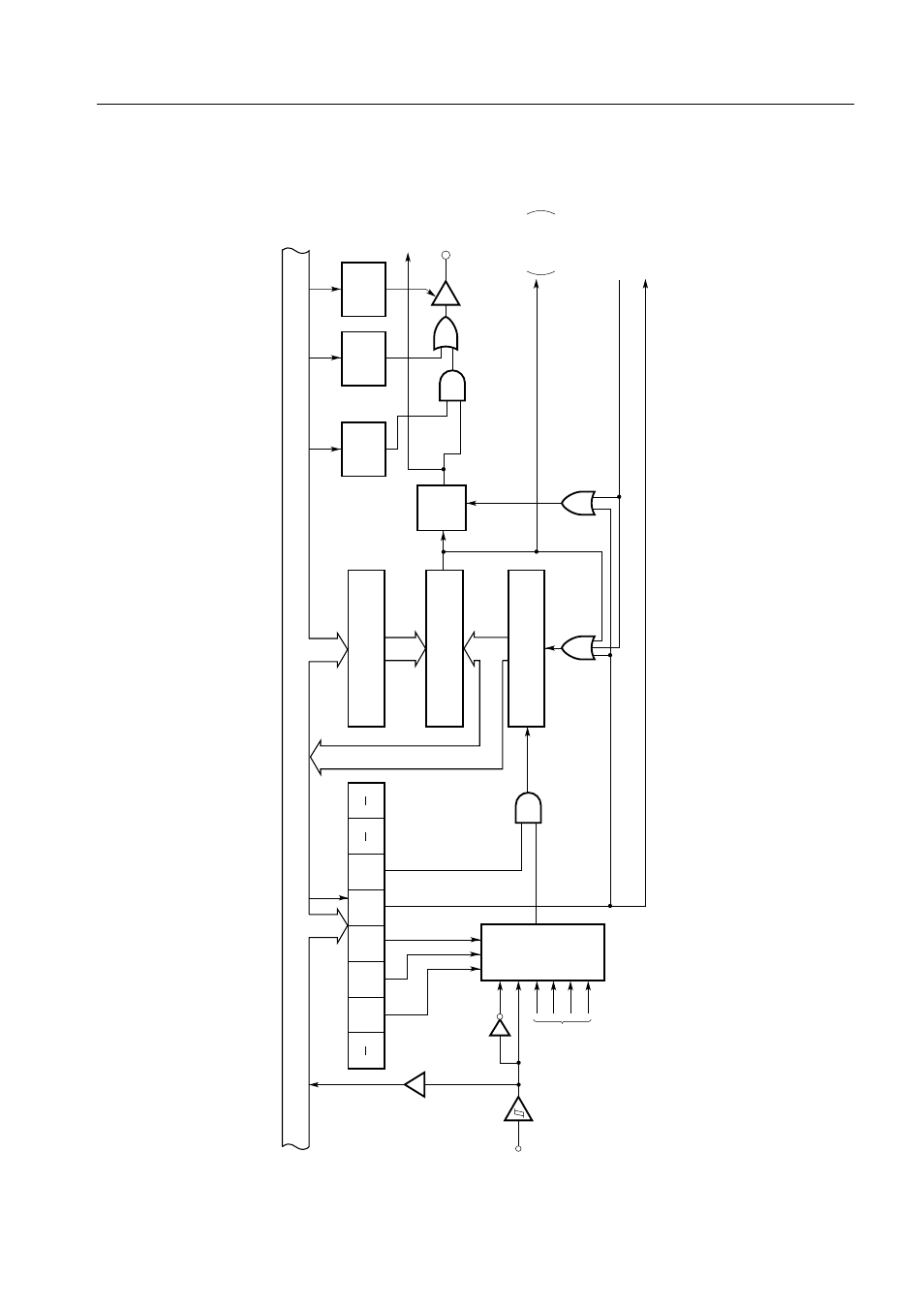

Figure 5-28. Block Diagram of the Timer/Event Counter (Channel 0)

Count register (8)

TI0

MPX

Timer operation start signal

8

8

8

From the

clock

generator

Internal bus

TM06

TM05

TM04

TM03

TM02

Port input

buffer

Comparator (8)

Modulo register (8)

TO enable

flag

P20

output

latch

signal

Port 2

input/

output

mode

Clear signal

T0

TMOD0

Bit 2 of PMGB

P20/PTO0

Output

buffer

Reset

RESET

IRQT0 clear

signal

TOUT

flip-flop

TM0

Input buffer

IRQT0

set signal

INTT0

PORT2.0

TOE0

To serial

interface

CP

Match

8

8

TOUT0