NEC PD750008 User Manual

Page 173

153

CHAPTER 5 PERIPHERAL HARDWARE FUNCTIONS

(a) Bus release signal (REL)

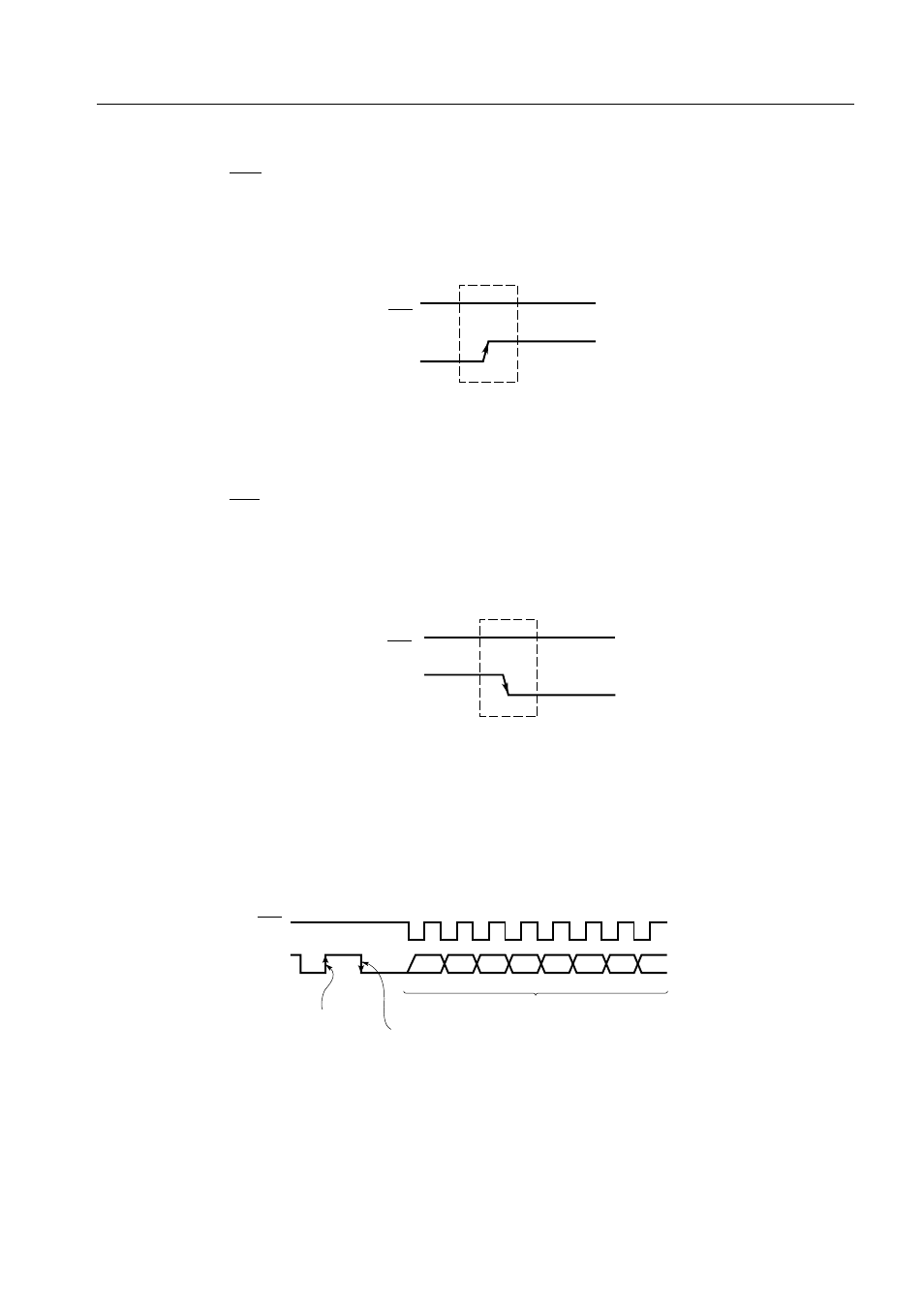

When the SCK line is high (the serial clock is not output), the SB0 (or SB1) line changes from low

to high. This signal is called the bus release signal, and is output by the master.

Figure 5-52. Bus Release Signal

This signal indicates that the master is to send an address to a slave. Slaves contain hardware to

detect the bus release signal.

(b) Command signal (CMD)

When the SCK line is high (the serial clock is not output), the SB0 (or SB1) line changes from high

to low. This signal is called the command signal, which is output by the master.

Figure 5-53. Command Signal

Slaves contain hardware to detect the command signal.

(c) Address

An address is 8-bit data and is output by the master to connected slaves to select a particular slave.

Figure 5-54. Address

The 8-bit data following the bus release signal or command signal is defined as an address. A slave

detects the condition for the addresses by hardware, and checks whether the 8-bit data matches the

number assigned to the slave (slave address). If the 8-bit data matches the slave address, that slave

is selected. The selected slave continues to communicate with the master until disconnection is

directed by the master.

SB0, SB1

"H"

SCK

SB0, SB1

"H"

SCK

SB0, SB1

1

2

3

4

5

6

7

8

Address

A7

A6

A5

A4

A3

A2

A1

A0

Command signal

Bus release signal

SCK