NEC PD750008 User Manual

Page 242

222

µPD750008 USER'S MANUAL

(2) Application of the HALT mode (at f

X

= 4.19 MHz)

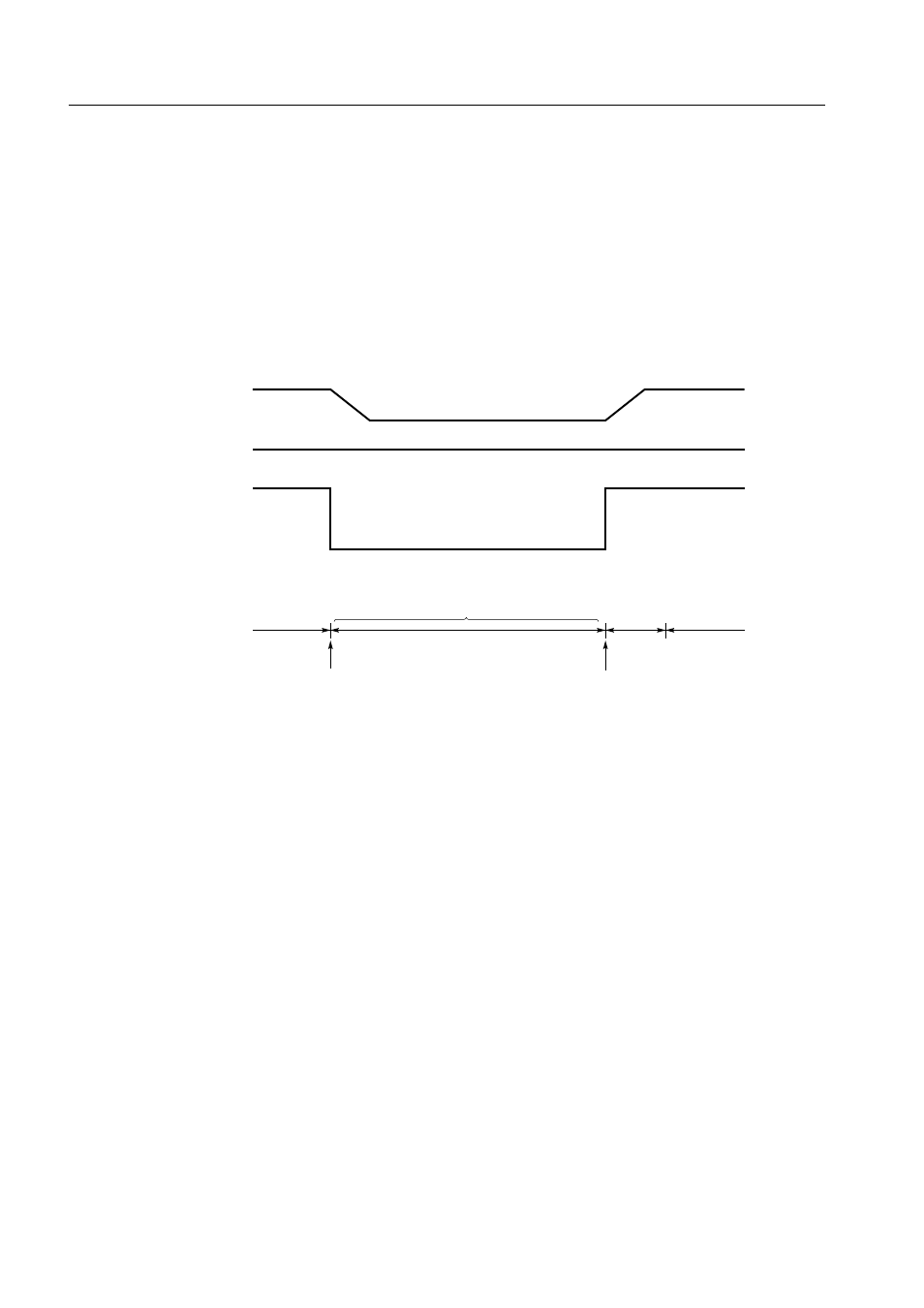

• The main system clock is switched to the subsystem clock on the falling edge of INT4.

• The oscillation of the main system clock is stopped, and HALT mode is set.

• In the standby mode, intermittent operation is performed at intervals of 0.5 s.

• The subsystem clock is switched back to the main system clock on the rising edge of INT4.

• INTBT is not used.

INT4

INT4

250 ms

Operating mode

(low-speed)

Intermittent operation

(HALT mode + low-speed operation)

Operating mode

V

DD

0 V

P00/INT4

CPU operation

Voltage on V

DD

Operating mode

(high-speed)