Pca9665, Nxp semiconductors – NXP Semiconductors PCA9665 User Manual

Page 72

PCA9665_2

© NXP B.V. 2006. All rights reserved.

Product data sheet

Rev. 02 — 7 December 2006

72 of 91

NXP Semiconductors

PCA9665

Fm+ parallel bus to I

2

C-bus controller

[1]

Parameters are valid over specified temperature and voltage range.

[2]

All voltage measurements are referenced to ground (GND). For testing, all inputs swing between 0 V and 3.0 V with a transition time of

5 ns maximum. All time measurements are referenced at input voltages of 1.5 V and output voltages shown in

and

.

[3]

Test conditions for outputs: C

L

= 50 pF; R

L

= 500

Ω

, except open-drain outputs.

Test conditions for open-drain outputs: C

L

= 50 pF; R

L

= 1 k

Ω

pull-up to V

DD

.

[4]

Initialization time for the serial interface after ENSIO bit goes HIGH in a write operation to the control register.

[5]

Resetting the device while actively communicating on the bus may cause glitches or an errant STOP condition.

[6]

Upon reset, the full delay will be the sum of t

rst

and the RC time constant of the SDA and SCL bus.

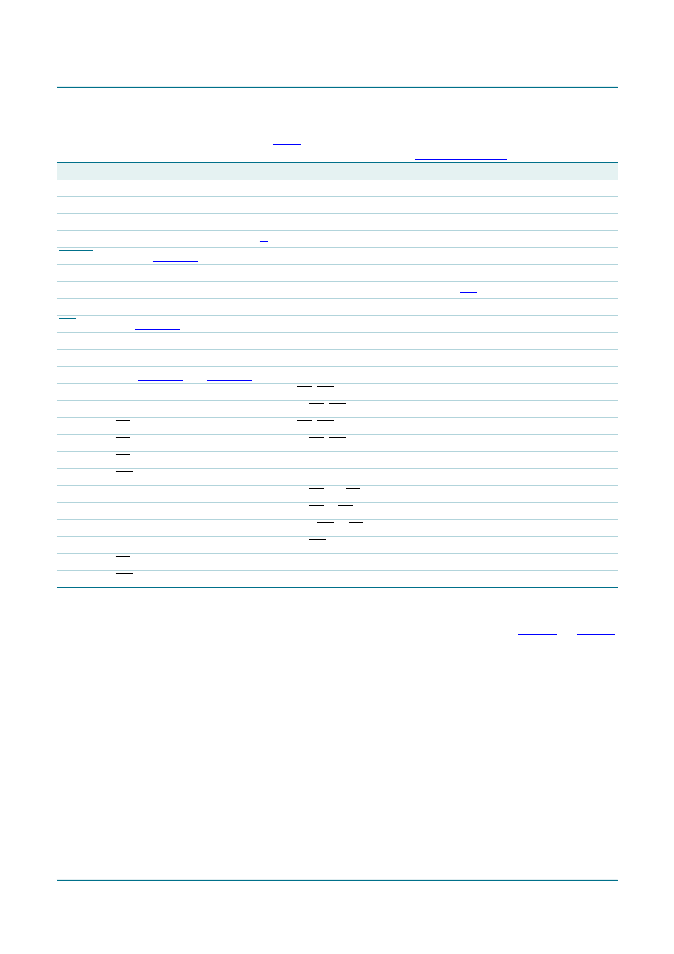

Table 50.

Dynamic characteristics (2.5 volt)

V

CC

= 2.5 V

±

0.2 V; T

amb

=

−

40

°

C to +85

°

C; unless otherwise specified. (See

for 3.3 V)

Symbol

Parameter

Conditions

Min

Typ

Max

Unit

Initialization timing

t

init(po)

power-on initialization time

-

-

550

µ

s

Serial interface initialization timing

t

init(sintf)

serial interface initialization time

from ENSIO bit HIGH

-

-

550

µ

s

RESET timing (see

t

w(rst)

reset pulse width

10

-

-

ns

t

rst

reset time

250

-

-

ns

t

rec(rst)

reset recovery time

0

-

-

ns

INT timing (see

)

t

as(int)

interrupt assert time

-

-

550

ns

t

das(int)

interrupt de-assert time

-

-

20

ns

Bus timing (see

t

su(A)

address setup time

to RD, WR LOW

0

-

-

ns

t

h(A)

address hold time

from RD, WR LOW

13

-

-

ns

t

su(CE_N)

CE setup time

to RD, WR LOW

0

-

-

ns

t

h(CE_N)

CE hold time

from RD, WR LOW

0

-

-

ns

t

w(RDL)

RD LOW pulse width

20

-

-

ns

t

w(WRL)

WR LOW pulse width

20

-

-

ns

t

d(DV)

data valid delay time

after RD and CE LOW

-

-

22

ns

t

d(QZ)

data output float delay time

after RD or CE HIGH

-

-

17

ns

t

su(Q)

data output setup time

before WR or CE HIGH (write cycle)

12

-

-

ns

t

h(Q)

data output hold time

after WR HIGH

0

-

-

ns

t

w(RDH)

RD HIGH pulse width

18

-

-

ns

t

w(WRH)

WR HIGH pulse width

18

-

-

ns