Pca9665 – NXP Semiconductors PCA9665 User Manual

Page 21

PCA9665_2

© NXP B.V. 2006. All rights reserved.

Product data sheet

Rev. 02 — 7 December 2006

21 of 91

NXP Semiconductors

PCA9665

Fm+ parallel bus to I

2

C-bus controller

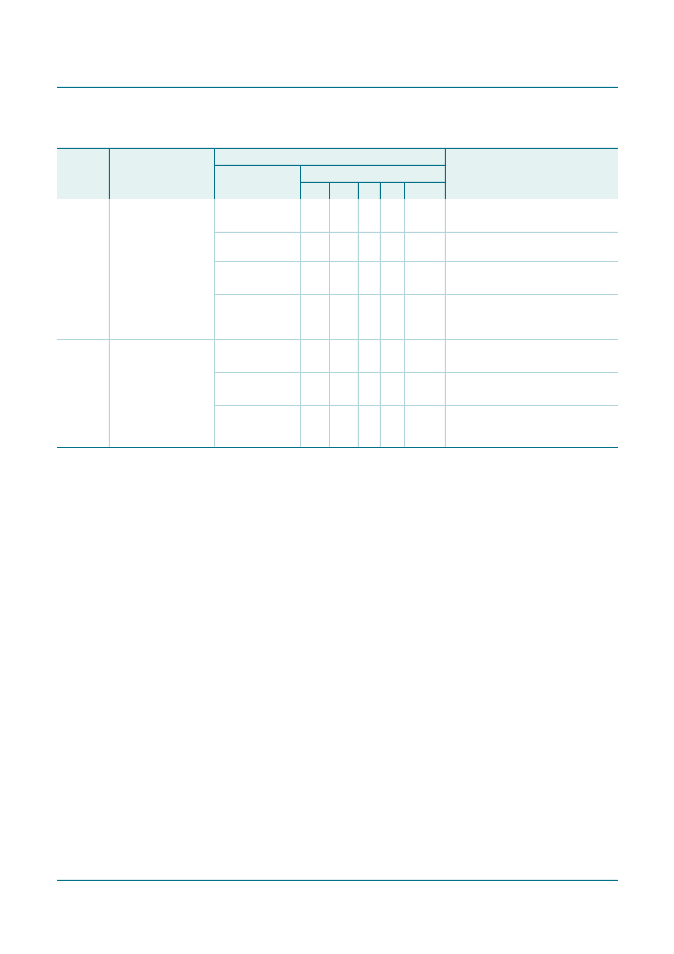

30h

Data byte in I2CDAT

has been transmitted;

NACK has been

received

Load data byte or 0

0

0

X

0

Data byte will be transmitted;

ACK/NACK will be received

no I2CDAT action

or

1

0

0

X

0

Repeated START will be transmitted;

no I2CDAT action

or

0

1

0

X

0

STOP condition will be transmitted;

STO flag will be reset

no I2CDAT action 1

1

0

X

0

STOP condition followed by a START

condition will be transmitted;

STO flag will be reset

38h

Arbitration lost in

SLA+W or Data bytes

No I2CDAT

action or

0

0

0

0

0

I

2

C-bus will be released;

PCA9665 will enter Slave mode.

No I2CDAT

action or

0

0

0

1

0

I

2

C-bus will be released;

PCA9665 will enter the Slave mode.

No I2CDAT

action

1

0

0

X

0

A START condition will be

transmitted when the bus becomes

free

Table 27.

Master Transmitter Byte mode (MODE = 0)

…continued

Status

code

(I2CSTA)

Status of the

I

2

C-bus and the

PCA9665

Application software response

Next action taken by the PCA9665

To/from I2CDAT

To I2CCON

STA STO SI

AA

MODE