Figure 22, Pca9665, Nxp semiconductors – NXP Semiconductors PCA9665 User Manual

Page 62

PCA9665_2

© NXP B.V. 2006. All rights reserved.

Product data sheet

Rev. 02 — 7 December 2006

62 of 91

NXP Semiconductors

PCA9665

Fm+ parallel bus to I

2

C-bus controller

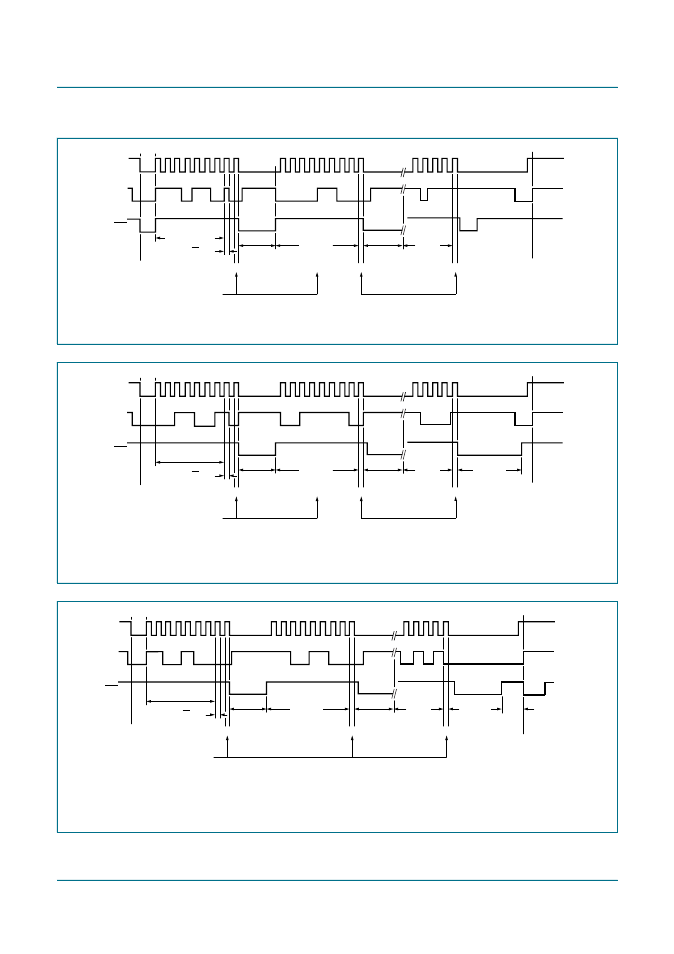

Master PCA9665 reads data from slave transmitter.

Fig 20. Bus timing diagram; Unbuffered Master Receiver mode

n byte

ACK

SCL

SDA

INT

START

condition

7-bit address

R/W = 1

interrupt

from slave

first byte

ACK

no ACK

interrupt

STOP

condition

002aab032

from master receiver

External master receiver reads data from PCA9665.

(1) As defined in I2CADR register.

Fig 21. Bus timing diagram; Unbuffered Slave Transmitter mode

n byte

ACK

SCL

SDA

INT

START

condition

7-bit address

(1)

R/W = 1

interrupt

from slave PCA9665

first byte

ACK

no ACK

interrupt

STOP

condition

002aab033

from master receiver

interrupt

Slave PCA9665 is written to by external master transmitter.

(1) As defined in I2CADR register.

Fig 22. Bus timing diagram; Unbuffered Slave Receiver mode

n byte

ACK

SCL

SDA

INT

START

condition

7-bit address

(1)

R/W = 0

interrupt

from slave PCA9665

first byte

ACK

ACK

interrupt

STOP

condition

002aab034

interrupt

interrupt

(after STOP)