11 reset, 12 i2c-bus timing diagrams, unbuffered mode, Section 8.11 “reset – NXP Semiconductors PCA9665 User Manual

Page 61: Pca9665, Nxp semiconductors, 12 i, C-bus timing diagrams, unbuffered mode

PCA9665_2

© NXP B.V. 2006. All rights reserved.

Product data sheet

Rev. 02 — 7 December 2006

61 of 91

NXP Semiconductors

PCA9665

Fm+ parallel bus to I

2

C-bus controller

8.11 Reset

Reset of the PCA9665 to its default state can be performed in 2 different ways:

•

By holding the RESET pin LOW for a minimum of t

w(rst)

.

•

By using the Parallel Software Reset sequence as described in

.

8.12 I

2

C-bus timing diagrams, Unbuffered mode

The diagrams (

through

) illustrate typical timing diagrams for the

PCA9665 in master/slave functions.

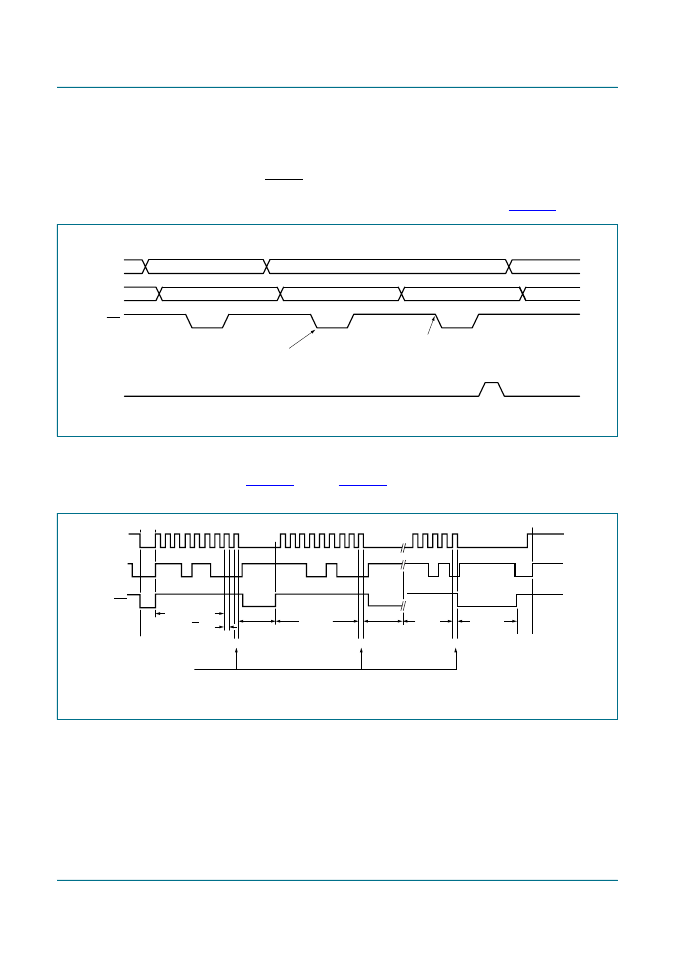

Fig 18. Parallel Software Reset sequence

002aab966

A[1:0]

00

10

access to INDPTR

Indirect Register pointer

access to the INDIRECT

Indirect Data field

D[7:0]

05h

I2CPRESET register selected

A5h

SWRST data byte 1

5Ah

SWRST data byte 2

WR

If D[7:0]

≠

A5h,

following byte is ignored

and reset is aborted.

If D[7:0]

≠

5Ah, reset is aborted.

If SWRST Data 1 = A5h and

SWRST Data 2 = 5Ah, PCA9665

is reset to its default state.

internal

reset

signal

Master PCA9665 writes data to slave transmitter.

Fig 19. Bus timing diagram; Unbuffered Master Transmitter mode

n byte

ACK

SCL

SDA

INT

START

condition

7-bit address

R/W = 0

interrupt

from slave receiver

first byte

ACK

ACK

interrupt

STOP

condition

002aab031

interrupt