3 slave receiver byte mode, Pca9665 – NXP Semiconductors PCA9665 User Manual

Page 25

PCA9665_2

© NXP B.V. 2006. All rights reserved.

Product data sheet

Rev. 02 — 7 December 2006

25 of 91

NXP Semiconductors

PCA9665

Fm+ parallel bus to I

2

C-bus controller

8.3.3 Slave Receiver Byte mode

In the Slave Receiver Byte mode, a number of data bytes are received from a master

transmitter one byte at a time (see

). To initiate the Slave Receiver mode, I2CADR

and I2CCON must be loaded as shown in

The upper 7 bits are the I

2

C-bus address to which PCA9665 will respond when addressed

by a master. GC is the control bit that allows the PCA9665 to respond or not to the

General Call address (00h).

When programmed to logic 1, the PCA9665 will acknowledge the General Call address.

When programmed to logic 0, the PCA9665 will not acknowledge the General Call

address.

ENSIO must be set to logic 1 to enable the I

2

C-bus interface. The AA bit must be set to

enable PCA9665 to acknowledge its own slave address, STA, STO, and SI must be reset.

When I2CADR and I2CCON have been initialized, the PCA9665 waits until it is addressed

by its own slave address followed by the data direction bit which must be ‘0’ (W) to operate

in the Slave Receiver mode. After its own slave address and the W bit have been

received, the Serial Interrupt flag (SI) is set, the Interrupt line (INT) goes LOW, and

I2CSTA is loaded with 60h. This status code is used to vector to an interrupt service

routine, and the appropriate action to be taken is detailed in

.

The Slave Receiver Buffered mode may also be entered when:

•

The arbitration is lost while the PCA9665 is in the master mode. See status 68h and

D8h.

•

The General Call Address (00h) has been received (General Call address enabled

with GC = 1). See status D0h.

If the AA bit is reset during a transfer, the PCA9665 will return a not acknowledge (logic 1)

on SDA after the next received data byte. While AA is reset, the I

2

C-bus state machine

does not respond to its own slave address. However, the I

2

C-bus is still monitored and

address recognition may be resumed at any time by setting AA. This means that the AA

bit may be used to temporarily isolate PCA9665 from the I

2

C-bus.

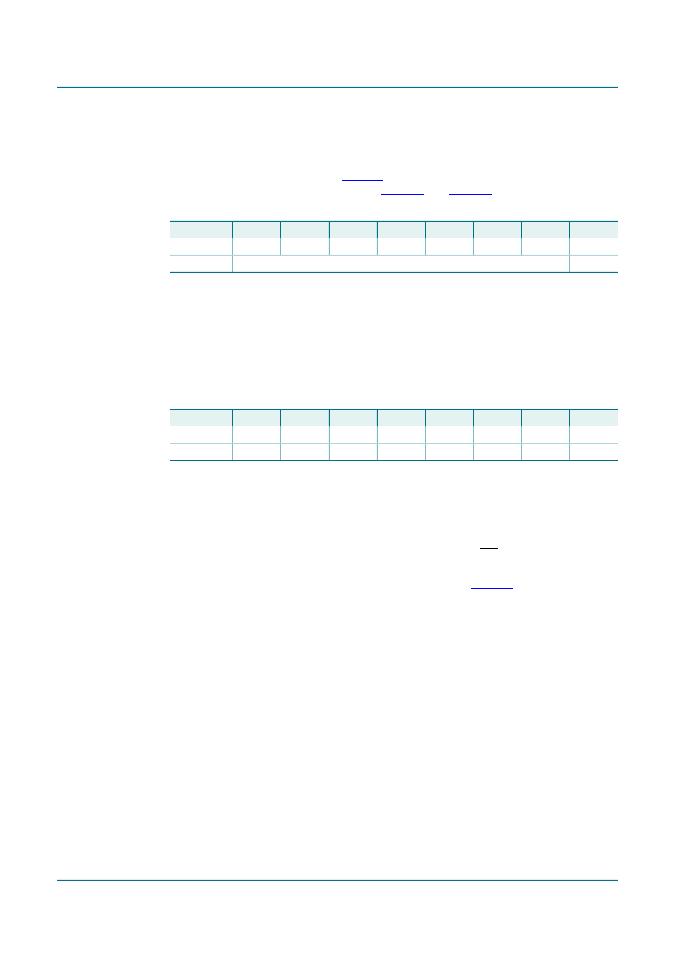

Table 29.

I2CADR initialization

Bit

7

6

5

4

3

2

1

0

Symbol

AD7

AD6

AD5

AD4

AD3

AD2

AD1

GC

Value

own slave address

X

Table 30.

I2CCON initialization

Bit

7

6

5

4

3

2

1

0

Symbol

AA

ENSIO

STA

STO

SI

-

-

MODE

Value

1

1

0

0

0

X

X

0