4 i2c-bus obstructed by a low level on scl or sda, Pca9665 – NXP Semiconductors PCA9665 User Manual

Page 59

PCA9665_2

© NXP B.V. 2006. All rights reserved.

Product data sheet

Rev. 02 — 7 December 2006

59 of 91

NXP Semiconductors

PCA9665

Fm+ parallel bus to I

2

C-bus controller

8.9.4 I

2

C-bus obstructed by a LOW level on SCL or SDA

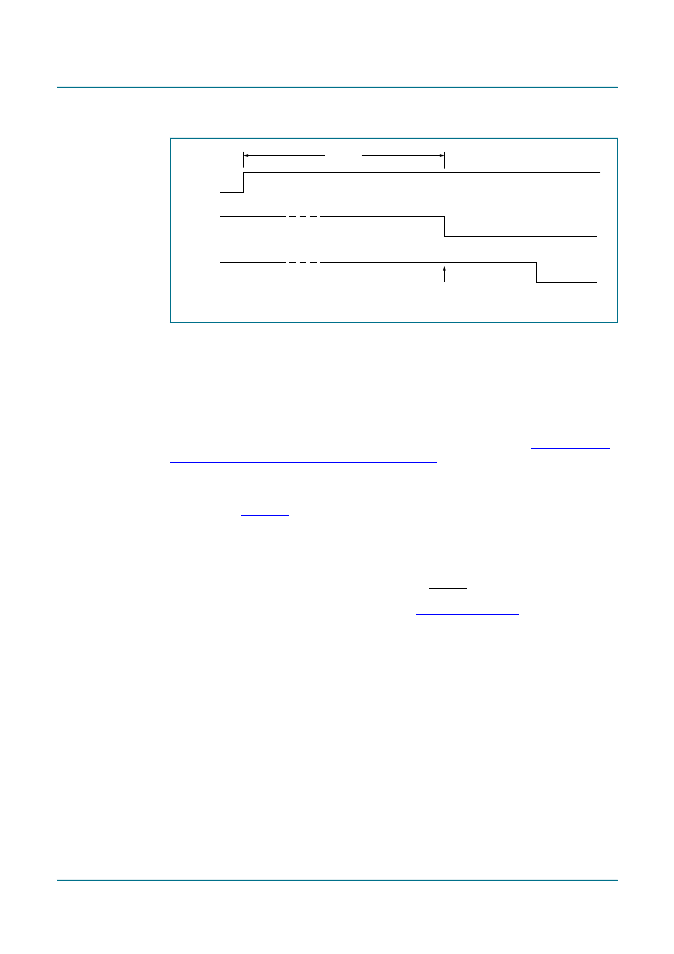

An I

2

C-bus hang-up occurs if SDA or SCL is pulled LOW by an uncontrolled source. If the

SCL line is obstructed (pulled LOW) by a device on the bus, no further serial transfer is

possible, and the PCA9665 cannot resolve this type of problem. When this occurs, the

problem must be resolved by the device that is pulling the SCL bus line LOW.

When the SCL line stays LOW for a period equal to the time-out value, the PCA9665

concludes that this is a bus error and behaves in a manner described in

“The Time-out register, I2CTO (indirect address 04h)”

.

If the SDA line is obstructed by another device on the bus (e.g., a slave device out of bit

synchronization), the problem can be solved by transmitting additional clock pulses on the

SCL line (see

). The PCA9665 sends out nine clock pulses followed by the

STOP condition. If the SDA line is released by the slave pulling it LOW, a normal START

condition is transmitted by the PCA9665, state 08h is entered and the serial transfer

continues. If the SDA line is not released by the slave pulling it LOW, then the PCA9665

concludes that there is a bus error, loads 70h in I2CSTA, generates an interrupt signal,

and releases the SCL and SDA lines. After the microcontroller reads the status register, it

needs to send a reset signal (hardware through the RESET pin, or software through the

parallel port) in order to reset the PCA9665. See

for more

information.

If a forced bus access occurs or a repeated START condition is transmitted while SDA is

obstructed (pulled LOW), the PCA9665 performs the same action as described above. In

each case, state 08h is entered after a successful START condition is transmitted and

normal serial transfer continues. Note that the CPU is not involved in solving these bus

hang-up problems.

Fig 16. Forced access to a busy I

2

C-bus

STA flag

SDA line

SCL line

time-out

START condition

002aab029