Figure 9, Pca9665, Nxp semiconductors – NXP Semiconductors PCA9665 User Manual

Page 26: Fm+ parallel bus to i, C-bus controller

PCA9665_2

© NXP B.V. 2006. All rights reserved.

Product data sheet

Rev. 02 — 7 December 2006

26 of 91

NXP Semiconductors

PCA9665

Fm+ parallel bus to I

2

C-bus controller

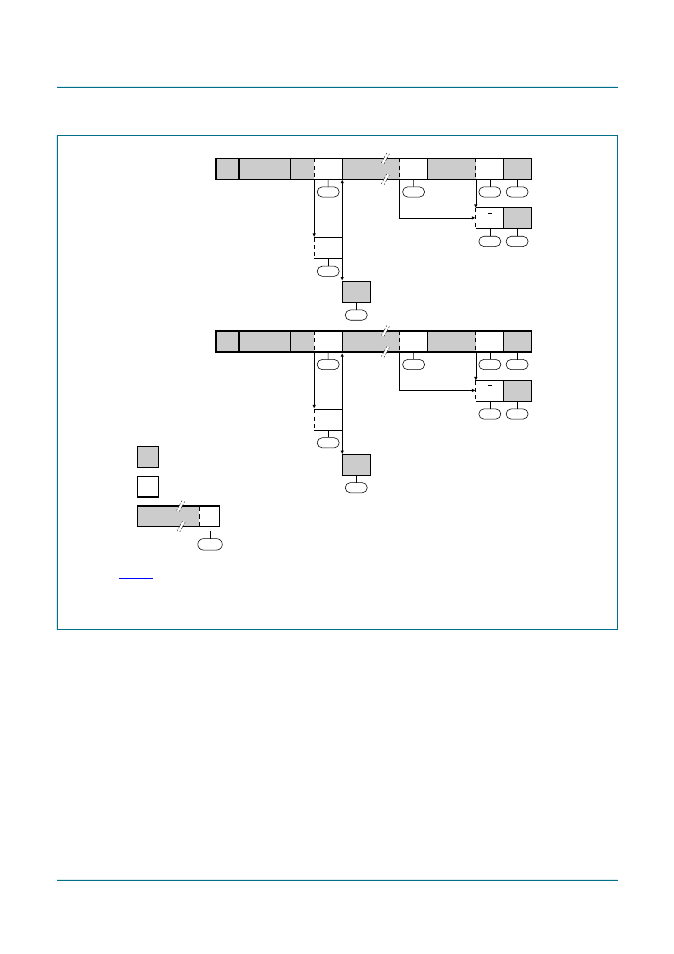

(1) See

(2) Defined state when a single byte is received and an ACK is sent (AA = 1).

(3) Defined state when a single byte is received and a NACK is sent (AA = 0).

Fig 9.

Format and states in the Slave Receiver Byte mode (MODE = 0)

S

SLA

W

A

DATA

A

P or S

60h

80h

A0h

A

68h

002aab026

reception of

own slave address

and one or more

data bytes;

all are Acknowledged.

last data byte received is

Not Acknowledged

arbitration lost as MST and

addressed as slave

DATA

A

80h

P or S

F8h

A

88h

on STOP

P or S

F8h on STOP

GENERAL

CALL = 00h

A

A

P or S

D0h

E0h

A0h

A

D8h

DATA

A

E0h

P or S

A

E8h

reception of the

General Call address

and one or more

data bytes

last data byte received is

Not Acknowledged

arbitration lost as MST and

addressed as slave by

General Call

S

F8h

on STOP

W

(2)

(2)

(3)

(2)

(2)

(3)

P or S

F8h on STOP

n

This number (contained in I2CSTA) corresponds

to a defined state of the I

2

C-bus.

(1)

A

any number of data bytes and

their associated Acknowledge bits

from master to slave

from slave to master

DATA

DATA