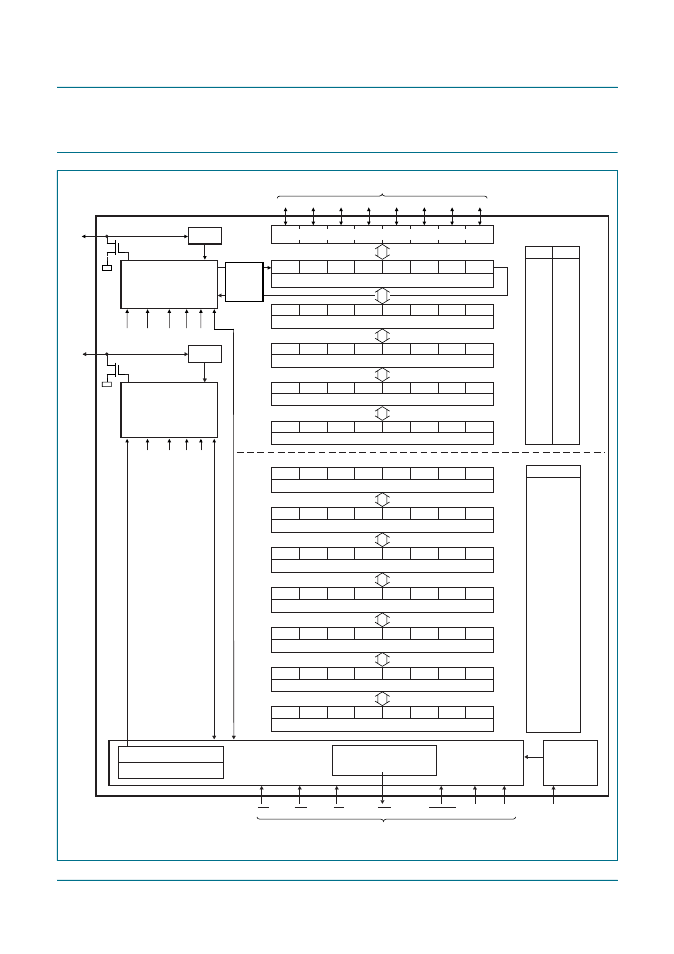

Block diagram, Pca9665, Nxp semiconductors – NXP Semiconductors PCA9665 User Manual

Page 3: Fm+ parallel bus to i, C-bus controller

PCA9665_2

© NXP B.V. 2006. All rights reserved.

Product data sheet

Rev. 02 — 7 December 2006

3 of 91

NXP Semiconductors

PCA9665

Fm+ parallel bus to I

2

C-bus controller

5.

Block diagram

Fig 1.

Block diagram of PCA9665

SD7

SD6

SD5

SD4

SD3

SD2

SD1

SD0

I2CDAT – data register – read/write

BUS BUFFER

SDA CONTROL

AA ENSIO STA STO SI

SCL CONTROL

ENSIO STA STO SI

FILTER

PCA9665

SDA

SCL

–

–

–

–

–

IP2

IP1

IP0

INDPTR – indirect address pointer – write only

ST5

ST4

ST3

ST2

ST1

ST0

0

0

I2CSTA – status register – read only

AA

ENSIO

STA

STO

SI

MODE

I2CCON – control register – read/write

CLOCK SELECTOR

OSCILLATOR

CONTROL BLOCK

CE

WR

RD

INT

RESET

A1

A0

V

DD

A1

A0

0

1

0

0

0

0

1

1

INTERRUPT CONTROL

POWER-ON

RESET

D7

D6

D5

D4

D3

D2

D1

D0

data

FILTER

control signals

002aab023

BIT7

BIT6

BIT5

BIT4

BIT3

BIT2

BIT1

BIT0

INDIRECT – indirect register access – read/write

1

0

direct registers

AD7

AD6

AD5

AD4

AD3

AD2

AD1

GC

I2CADR – own address – read/write

L7

L6

L5

L4

L3

L2

L1

L0

I2CSCLL – SCL LOW period – read/write

H7

H6

H5

H4

H3

H2

H1

H0

I2CSCLH – SCL HIGH period – read/write

TE

BIT6

BIT5

BIT4

BIT3

BIT2

BIT1

BIT0

I2CTO – TIMEOUT register – read/write

indirect registers

00h

01h

02h

03h

INDPTR

LB

BC6

BC5

BC2

BC1

BC0

I2CCOUNT – byte count – read/write

BC4

BC3

IR7

IR6

IR5

IR4

IR3

IR2

IR1

IR0

I2CPRESET – software reset register – write only

04h

05h

–

–

–

AC0

I2CMODE – I

2

C-bus mode register – read/write

–

–

–

–

–

AC1

06h

68-BYTE

BUFFER