13 i2c-bus timing diagrams, buffered mode, Pca9665, Nxp semiconductors – NXP Semiconductors PCA9665 User Manual

Page 63: 13 i, C-bus timing diagrams, buffered mode

PCA9665_2

© NXP B.V. 2006. All rights reserved.

Product data sheet

Rev. 02 — 7 December 2006

63 of 91

NXP Semiconductors

PCA9665

Fm+ parallel bus to I

2

C-bus controller

8.13 I

2

C-bus timing diagrams, Buffered mode

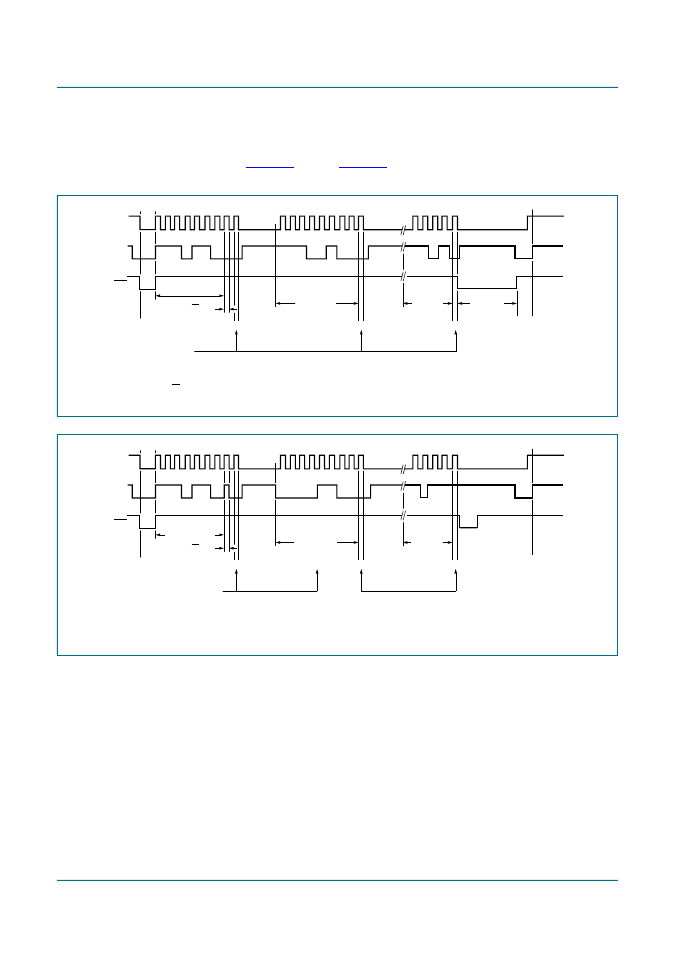

The diagrams (

through

) illustrate typical timing diagrams for the

PCA9665 in master/slave functions.

Master PCA9665 writes data to slave transmitter.

(1) 7-bit address + R/W = 0 byte and number of bytes sent = value programmed in I2CCOUNT register (BC[6:0]

≤

68).

Fig 23. Bus timing diagram; Buffered Master Transmitter mode

n byte

(1)

ACK

SCL

SDA

INT

START

condition

7-bit address

(1)

R/W = 0

from slave receiver

first byte

(1)

ACK

ACK

STOP

condition

002aab267

interrupt

Master PCA9665 reads data from slave transmitter.

(1) Number of bytes received = value programmed in I2CCOUNT register (BC[6:0]

≤

68).

Fig 24. Bus timing diagram; Buffered Master Receiver mode

n byte

(1)

ACK

SCL

SDA

INT

START

condition

7-bit address

R/W = 1

from slave

first byte

(1)

ACK

no ACK

STOP

condition

002aab268

from master receiver