Pinning information, 1 pinning, Pca9665 – NXP Semiconductors PCA9665 User Manual

Page 4: Nxp semiconductors, Fm+ parallel bus to i, C-bus controller

PCA9665_2

© NXP B.V. 2006. All rights reserved.

Product data sheet

Rev. 02 — 7 December 2006

4 of 91

NXP Semiconductors

PCA9665

Fm+ parallel bus to I

2

C-bus controller

6.

Pinning information

6.1 Pinning

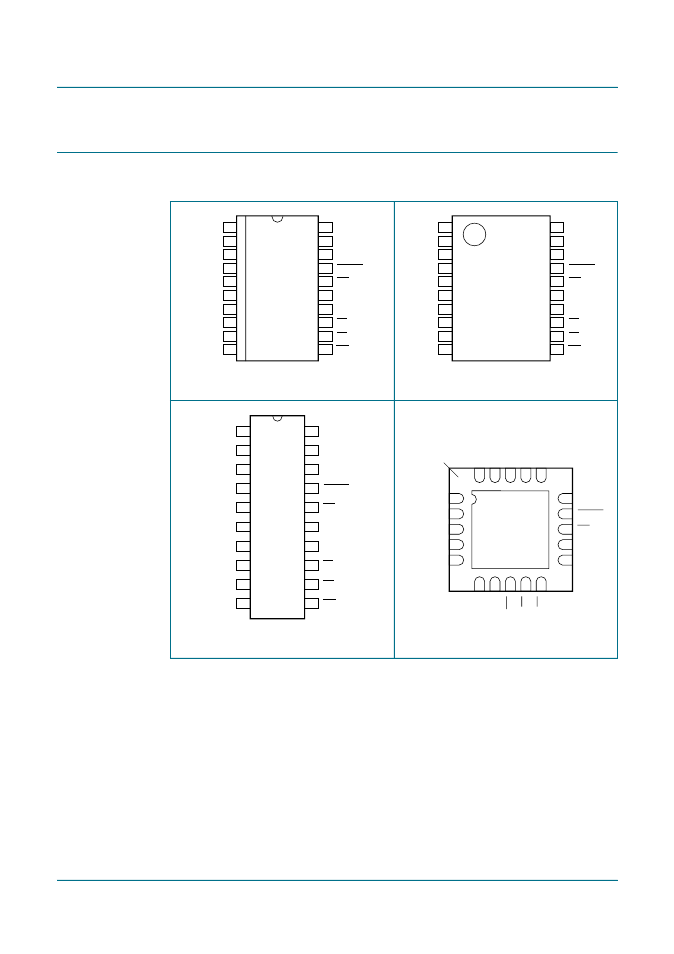

Fig 2.

Pin configuration of SO20

Fig 3.

Pin configuration of TSSOP20

Fig 4.

Pin configuration of DIP20

Fig 5.

Pin configuration of HVQFN20

PCA9665D

V

SS

002aab020

D0

D1

D2

D3

D4

D5

D6

D7

i.c.

1

2

3

4

5

6

7

8

9

10

12

11

14

13

16

15

18

17

20

19

V

DD

SDA

SCL

RESET

INT

A1

A0

CE

RD

WR

PCA9665PW

D0

002aab021

1

2

3

4

5

6

7

8

9

10

12

11

14

13

16

15

18

17

20

19

V

SS

D1

D2

D3

D4

D5

D6

D7

i.c.

V

DD

SDA

SCL

RESET

INT

A1

A0

CE

RD

WR

PCA9665N

D0

V

DD

D1

SDA

D2

SCL

D3

RESET

D4

INT

D5

A1

D6

A0

D7

CE

i.c.

RD

V

SS

WR

002aab019

1

2

3

4

5

6

7

8

9

10

12

11

14

13

16

15

18

17

20

19

002aab022

PCA9665BS

Transparent top view

A0

D6

D7

A1

D5

INT

D4

RESET

D3

SCL

i.c.

V

SS

WR

RD

CE

D2

D1

D0

V

DD

SDA

5

11

4

12

3

13

2

14

1

15

6

7

8

9

10

20

19

18

17

16

terminal 1

index area