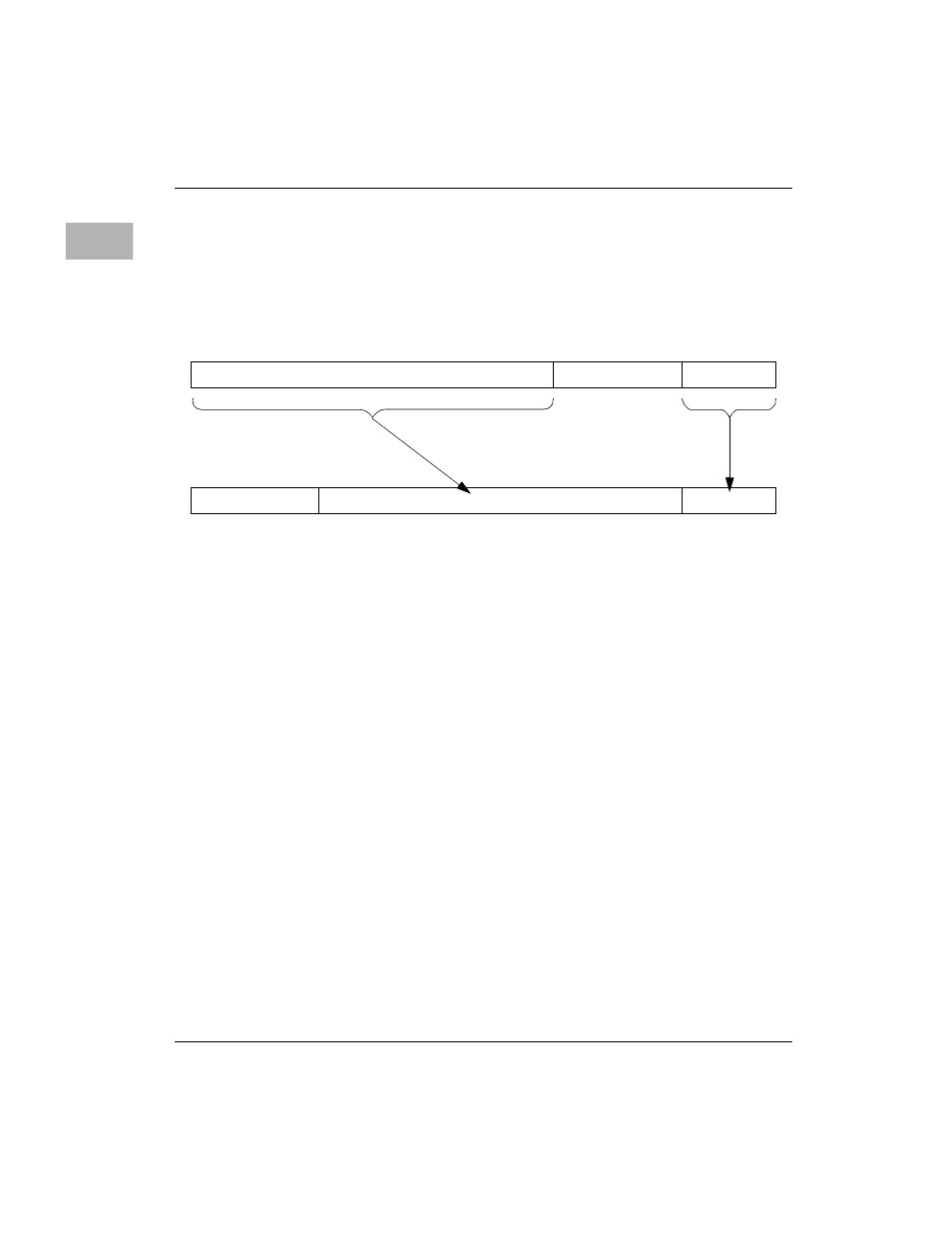

Figure 2-6. pci spread i/o address translation -22 – Motorola MVME2300 Series User Manual

Page 92

2-22

Computer Group Literature Center Web Site

Raven PCI Bridge ASIC

2

The Raven will perform spread I/O addressing when the MEM bit is clear

and the IOM bit is set. The Raven will take the MPC address, apply the

offset specified in the MSOFFx register, and map the result to PCI as

shown in

.

.

Figure 2-6. PCI Spread I/O Address Translation

Spread I/O addressing allows each PCI device’s I/O registers to reside on

a different MPC memory page, so device drivers can be protected from

each other using memory page protection.

All I/O accesses must be performed within natural word boundaries. Any

I/O access that is not contained within a natural word boundary will result

in unpredictable operation. For example, an I/O transfer of four bytes

starting at address $80000010 is considered a valid transfer. An I/O

transfer of four bytes starting at address $80000011 is considered an

invalid transfer since it crosses the natural word boundary at address

$80000013/$80000014.

Generating PCI Configuration Cycles

The Raven uses configuration mechanism #1 as defined in PCI Local Bus

Specification 2.0 to generate configuration cycles. Please refer to the

specification for a complete description of this function.

1915 9702

MPC Address + Offset

31

12 11

5 4

0

31

0

PCI Address

25 24

0 0 0 0 0 0 0

0

0

0

0

0

0

0

5 4