Mpc error status register, Mpc error status register -39 – Motorola MVME2300 Series User Manual

Page 109

Raven Registers

http://www.motorola.com/computer/literature

2-39

2

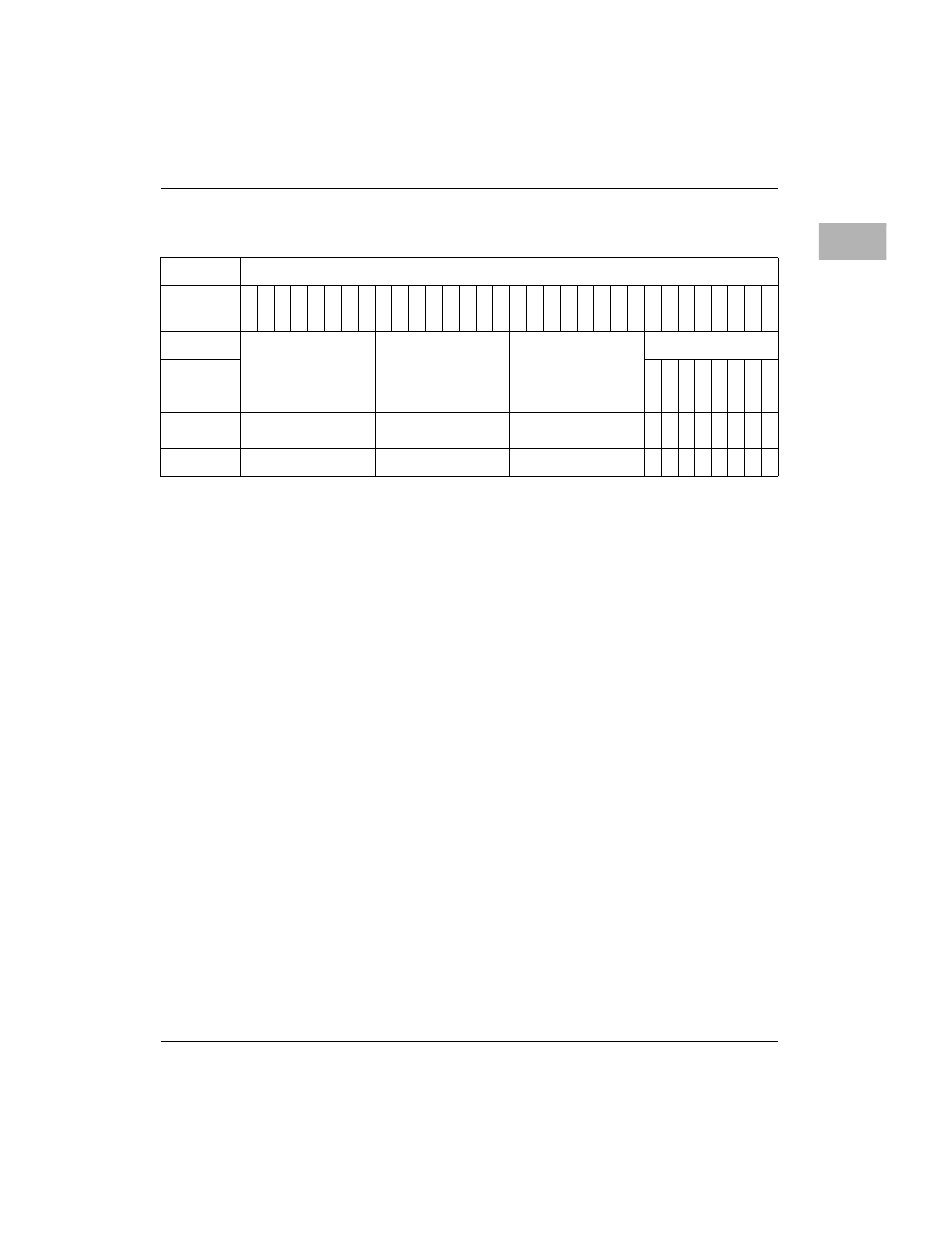

MPC Error Status Register

OVF

Error Status Overflow. This bit is set when an error is

detected and any of the error status bits are already set.

The bit may be cleared by writing a 1 to it; writing a 0 to

it has no effect.

MATO

MPC Address bus Time-Out. This bit is set when the

MPC address bus timer times out. The bit may be cleared

by writing it to a 1; writing it to a 0 has no effect. When

the MATOM bit in the MEREN register is set, the

assertion of this bit will assert MCHK to the master

designated by the MID field in the MERAT register. When

the MATOI bit in the MEREN register is set, the assertion

of this bit will assert an interrupt through the MPIC

interrupt controller.

PERR

PCI Parity Error. This bit is set when the PCI PERR

∗

pin

is asserted. The bit may be cleared by writing it to a 1;

writing it to a 0 has no effect. When the PERRM bit in the

MEREN register is set, the assertion of this bit will assert

MCHK to the master designated by the DFLT bit in the

MERAT register. When the PERRI bit in the MEREN

register is set, the assertion of this bit will assert an

interrupt through the MPIC interrupt controller.

Address

$FEFF0024

Bit

0 1 2 3 4 5 6 7 8 9

1

0

1

1

1

2

1

3

1

4

1

5

1

6

1

7

1

8

1

9

2

0

2

1

2

2

2

3

2

4

2

5

2

6

2

7

2

8

2

9

3

0

3

1

Name

MERST

OVF

MA

T

O

PERR

SERR

SMA

RT

A

Operation

R

R

R

R/

C

R

R/

C

R

R/

C

R/

C

R/

C

R/

C

Reset

$00

$00

$00

0

0

0

0

0

0

0

0