Interrupt acknowledge registers, End-of-interrupt registers – Motorola MVME2300 Series User Manual

Page 156

2-86

Computer Group Literature Center Web Site

Raven PCI Bridge ASIC

2

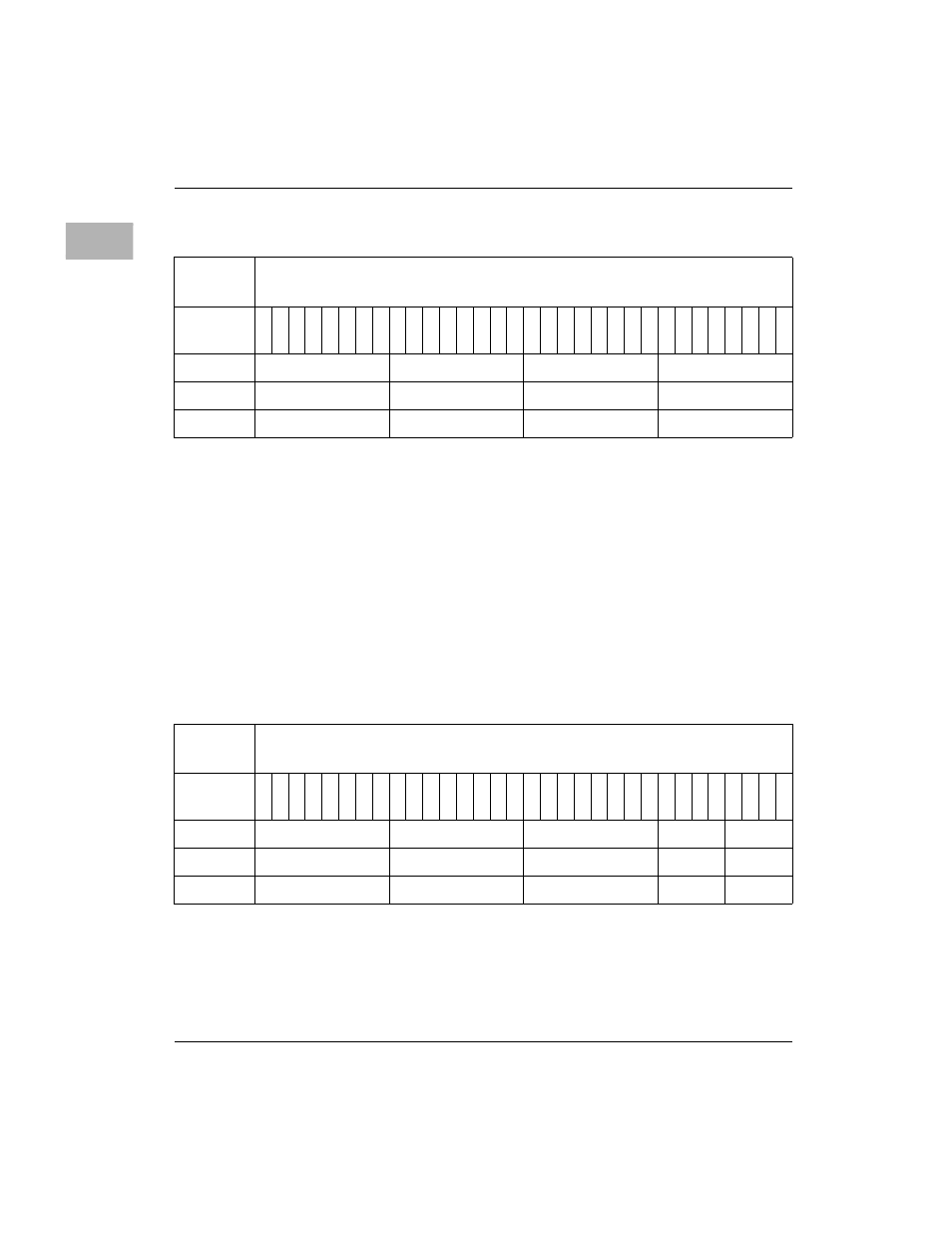

Interrupt Acknowledge Registers

On PowerPC-based systems, Interrupt Acknowledge is implemented as a

read request to a memory-mapped Interrupt Acknowledge register.

Reading the Interrupt Acknowledge register returns the interrupt vector

corresponding to the highest-priority pending interrupt. Reading this

register also has the following side effects.

❏

The associated bit in the Interrupt Pending register is cleared.

❏

Reading this register will update the In-Service register.

Reading this register without a pending interrupt will return a value of $FF

hexadecimal.

End-of-Interrupt Registers

EOI

End Of Interrupt. There is one EOI register per

processor. EOI code values other than 0 are currently

undefined. Data values written to this register are ignored;

zero is assumed. Writing to this register signals the end of

Offset

Processor 0 $200A0

Processor 1 $210A0

Bit

3

1

3

0

2

9

2

8

2

7

2

6

2

5

2

4

2

3

2

2

2

1

2

0

1

9

1

8

1

7

1

6

1

5

1

4

1

3

1

2

1

1

1

0 9 8 7 6 5 4 3 2 1 0

Name

VECTOR

Operation

R

R

R

R

Reset

$00

$00

$00

$FF

Offset

Processor 0 $200B0

Processor 1 $210B0

Bit

3

1

3

0

2

9

2

8

2

7

2

6

2

5

2

4

2

3

2

2

2

1

2

0

1

9

1

8

1

7

1

6

1

5

1

4

1

3

1

2

1

1

1

0 9 8 7 6 5 4 3 2 1 0

Name

EOI

Operation

R

R

R

R

W

Reset

$00

$00

$00

$0

$0