Ecc control register, Ecc control register -36 – Motorola MVME2300 Series User Manual

Page 198

3-36

Computer Group Literature Center Web Site

Falcon ECC Memory Controller Chip Set

3

The output of the chip prescale counter is used by the

refresher/scrubber and the 32-bit counter. After power-up,

this register is initialized to $42 (for 66MHz).

por

por is set by the occurrence of power-up reset. It is cleared

by writing a 1 to it. Writing a 0 to it has no effect.

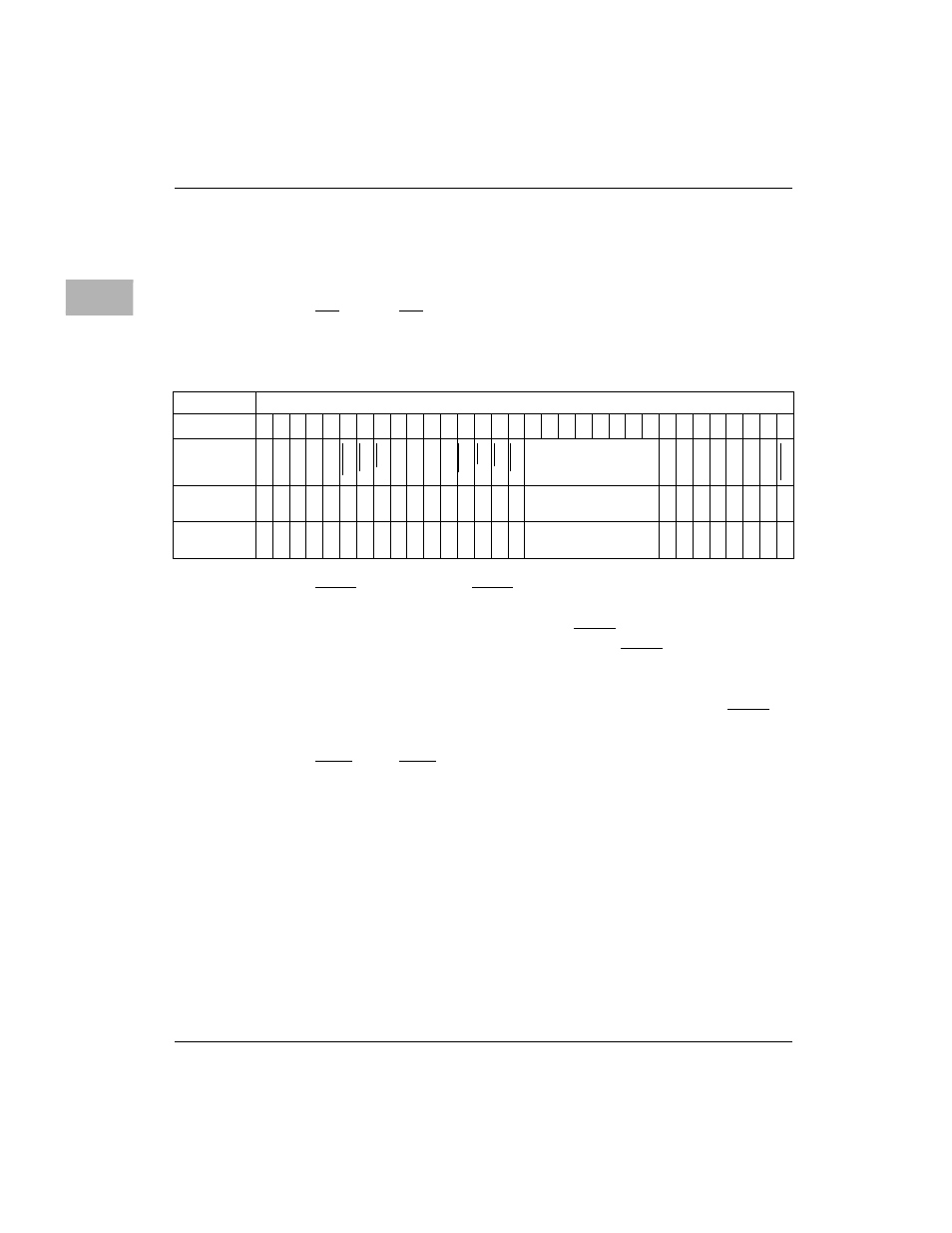

ECC Control Register

refdis

When set, refdis causes the refresher and all of its

associated counters and state machines to be cleared and

maintained that way until refdis is removed (cleared). If a

refresh cycle is in process when refdis is updated by a

write to this register, the update does not take effect until

the refresh cycle has completed. This prevents the

generation of illegal cycles to the DRAM when refdis is

updated.

rwcb

rwcb, when set, causes reads and writes to DRAM from

the PowerPC 60x bus to access check-bit data rather than

normal data. The data path used for this mode is DH24-31

for check-bit data controlled by the upper Falcon, and

DL24-31 for check-bit data controlled by the lower

Falcon. Each 8-bit check-bit location services 64 bits of

normal data. The 64 bits of data are all within the same

Falcon. Each Falcon provides every other 32 bits of data

in the normal mode. The following figure shows the

relationship between normal data and check-bit data.

Address

$FEF80028

Bit

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

Name

0

0

0

0

0

refd

is

rwcb

de

rc

0

0

0

0

scien

tie

n

sien

mi

en

0

0

0

0

0

0

0

mc

ken

Operation

R

R

R

R

R

R/W

R/W

R/W

R

R

R

R

R/W

R/W

R/W

R/W

READ ZERO

R

R

R

R

R

R

R

R/W

Reset

X

X

X

X

X

0 PL

0 PL

1 PL

X

X

X

X

0 PL

0 PL

0 PL

0 PL

X

X

X

X

X

X

X

X

0 P

L