Error address register, Error address register -42 – Motorola MVME2300 Series User Manual

Page 204

3-42

Computer Group Literature Center Web Site

Falcon ECC Memory Controller Chip Set

3

bit error (independent of the state of the elog bit). It is

cleared by power-up reset and by software writing all 0s

to it. When SBE COUNT rolls over from $FF to $00, its

Falcon sets the scof bit. It also pulses the INT_ signal low

if the scien bit is set.

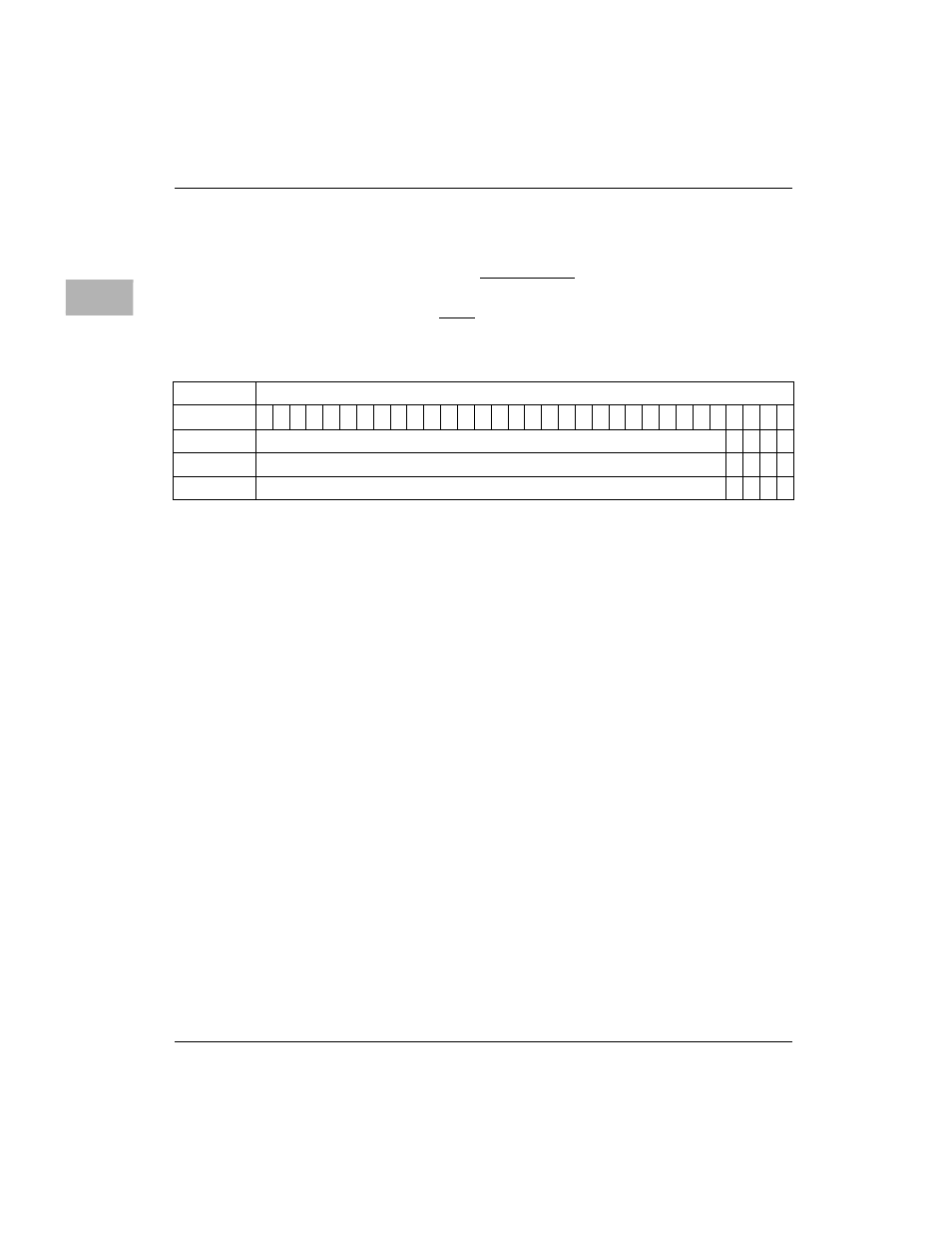

Error Address Register

ERROR_ADDRESS

These bits reflect the value that corresponds to bits 0-27

of the PowerPC 60x address bus when their Falcon last

logged an error during a PowerPC access to DRAM. They

reflect the value of the DRAM row and column addresses

if the error was logged during a scrub cycle. In this case,

bits 2-14 correspond to row address signals 0-12

respectively and bits 15-27 correspond to column address

signals 0-12 respectively. Refer to

in the Sizing

DRAM subsection under Software Considerations. It

shows how PowerPC addresses correspond to DRAM row

and column addresses.

3Falcon ECC Memory Controller Chip Set

0Programming Model

Address

$FEF80038

Bit

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

Name

ERROR_ADDRESS

0

0

0

0

Operation

READ ONLY

R

R

R

R

Reset

X P

X

X

X

X