Appendix a i/o map – FUJITSU Semiconductor Controller MB89950/950A User Manual

Page 278

264

APPENDIX

APPENDIX A

I/O Map

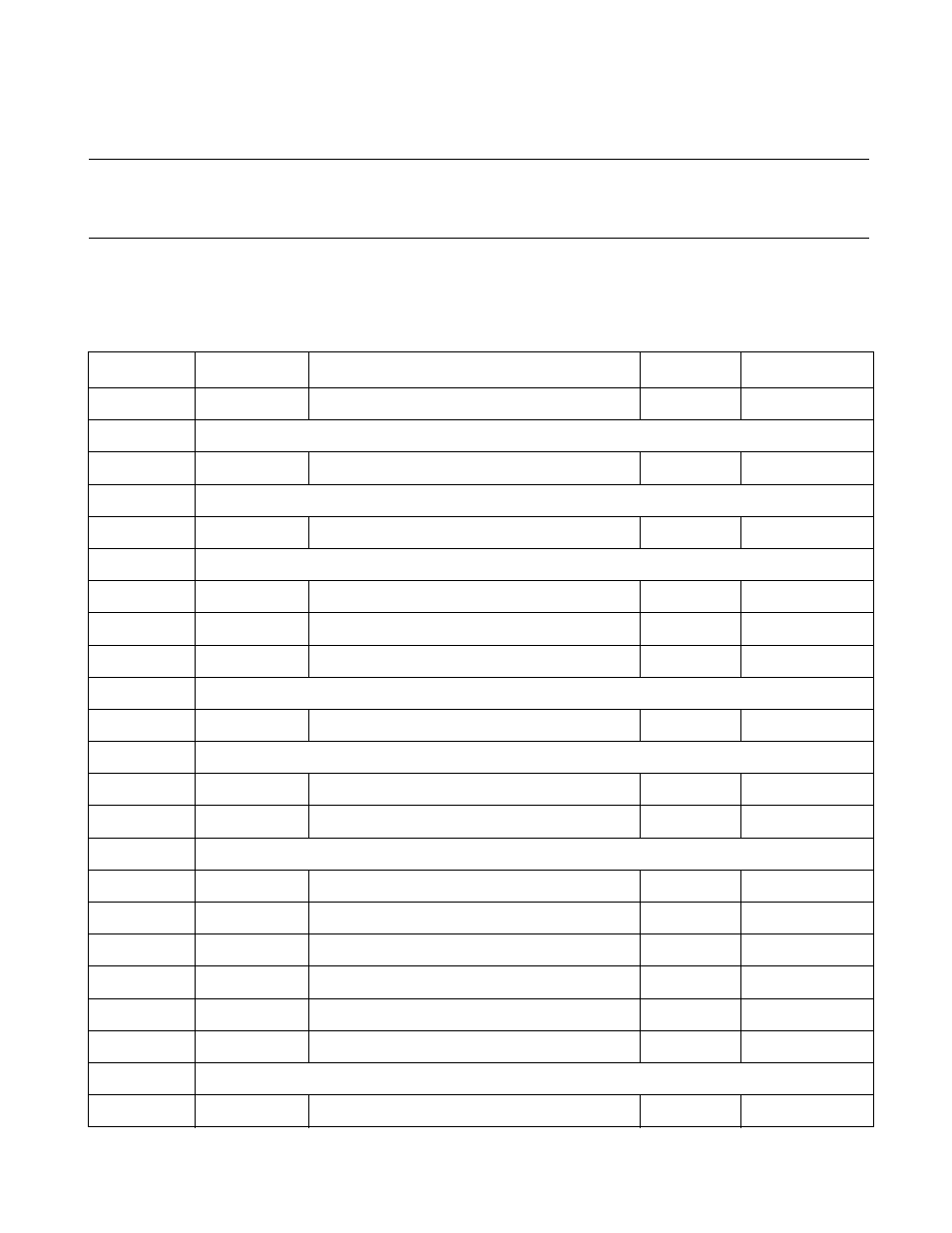

Table A-1 "I/O map" lists the addresses of the registers of used by the internal

peripheral functions of the MB89950/950A series.

■ I/O map

Table A-1 I/O map (1/2)

Address

Register name

Register description

Read/Write

Initial value

00

H

PDR0

Port 0 data register

R/W

11111111

B

01

H

(Vacancy)

02

H

PDR1

Port 1 data register

R/W

11111111

B

03

H

(Vacancy)

04

H

PDR2

Port 2 data register

R/W

--111111

B

05

H

to 07

H

(Vacancy)

08

H

STBC

Standby control register

R/W

0001----

B

09

H

WDTC

Watchdog timer control register

W

----XXXX

B

0A

H

TBTC

Timebase timer control register

R/W

---00000

B

0B

H

(Vacancy)

0C

H

PDR3

Port 3 data register

R/W

----1111

B

0D

H

(Vacancy)

0E

H

PDR4

Port 4 data register

R/W

-XXXXXXX

B

0F

H

DDR4

Port 4 direction register

W

-0000000

B

10

H

to 11

H

(Vacancy)

12

H

CNTR

PWM timer control register

R/W

0-000000

B

13

H

COMR

PWM timer compare register

W

XXXXXXXX

B

14

H

PCR1

PWC pulse width control register 1

R/W

0-0--000

B

15

H

PCR2

PWC pulse width control register 2

R/W

000-0000

B

16

H

RLBR

PWC reload buffer register

R/W

XXXXXXXX

B

17

H

NCCR

PWC noise filter control register

R/W

------00

B

18

H

to 1B

H

(Vacancy)

1C

H

SMR

Serial mode register

R/W

00000000

B