3 serial status and data register (ssd) – FUJITSU Semiconductor Controller MB89950/950A User Manual

Page 223

209

CHAPTER 10 UART

10.4.3

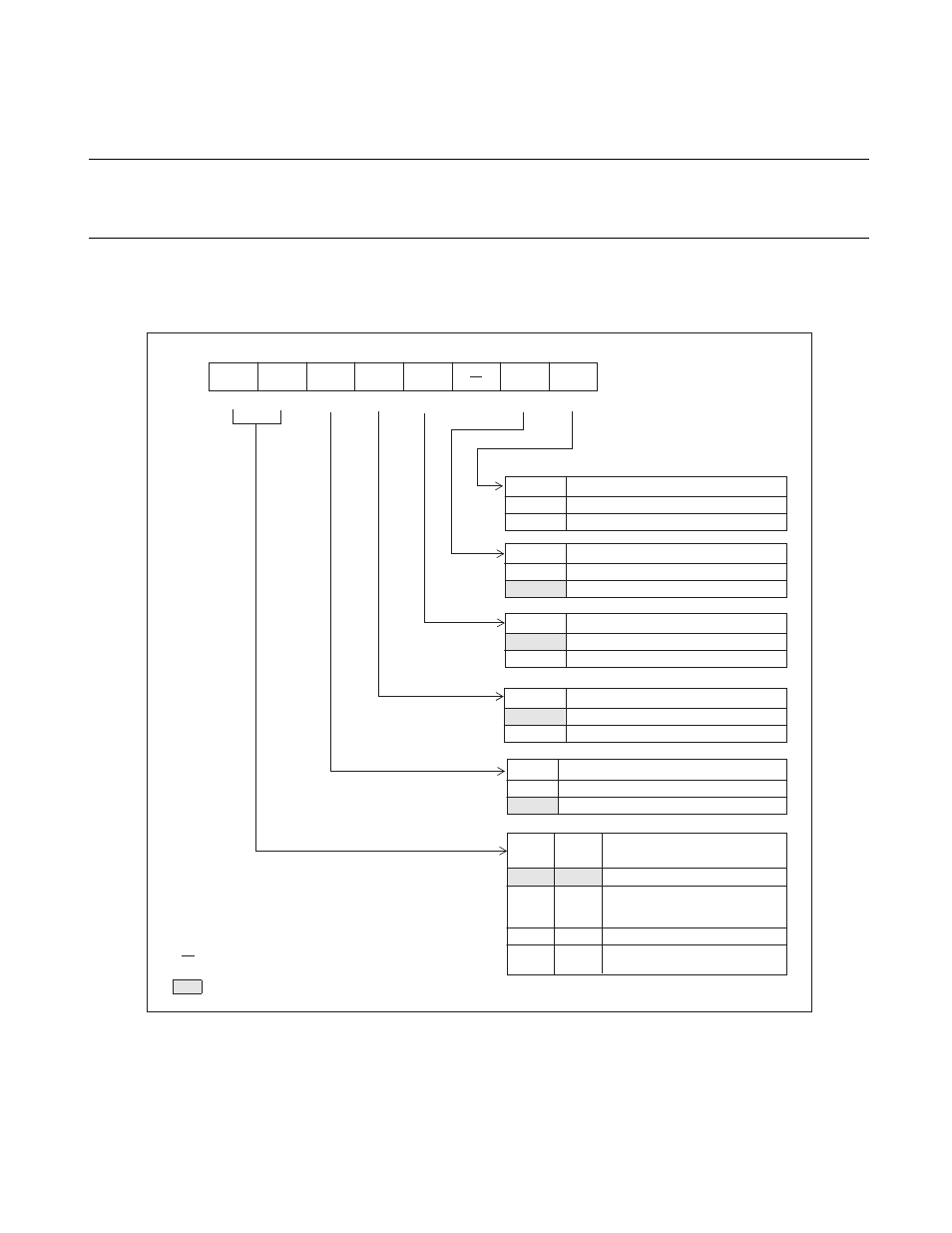

Serial Status and Data Register (SSD)

The serial status and data register (SSD) is used to set and monitor transmit/receive

operation and error status.

■ Serial status and rate register (SSD)

Figure 10.4-4 Serial status and data register (SSD)

Address

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

Initial value

0022

H

RDRF

ORFE

TDRE

TIE

RIE

TD8/TP RD8/RP

00100-1X

B

R

R

R

R/W

R/W

R/W

R

RD8/RP

Received data parity selection bit

Transmitted data parity selection bit

Receiver interrupt enable bit

Transmitter interrupt enable bit

Transmission data register empty bit

Receive data flag bit/Error flag bit

0

Odd parity

1

Even parity

TD8/TP

0

Odd parity

1

Even parity

RIE

0

Disables interrupt

1

Enables interrupt

Enables interrupt

TIE

0

Disables interrupt

1

TDRE

0

Full of transmission data

1

Empty

RDRF

ORFE

0

0

No data

0

1

Framing error

(When new data is received at

this state, RDRF will not be set)

1

0

Normal data

1

1

Overrun error (Previous data

remains)

R

: Read-only

: Unused

X

: Indeterminate

—

: Initial value

R/W : Readable and writable