Operation of timebase timer – FUJITSU Semiconductor Controller MB89950/950A User Manual

Page 122

108

CHAPTER 5 TIMEBASE TIMER

■ Operation of timebase timer

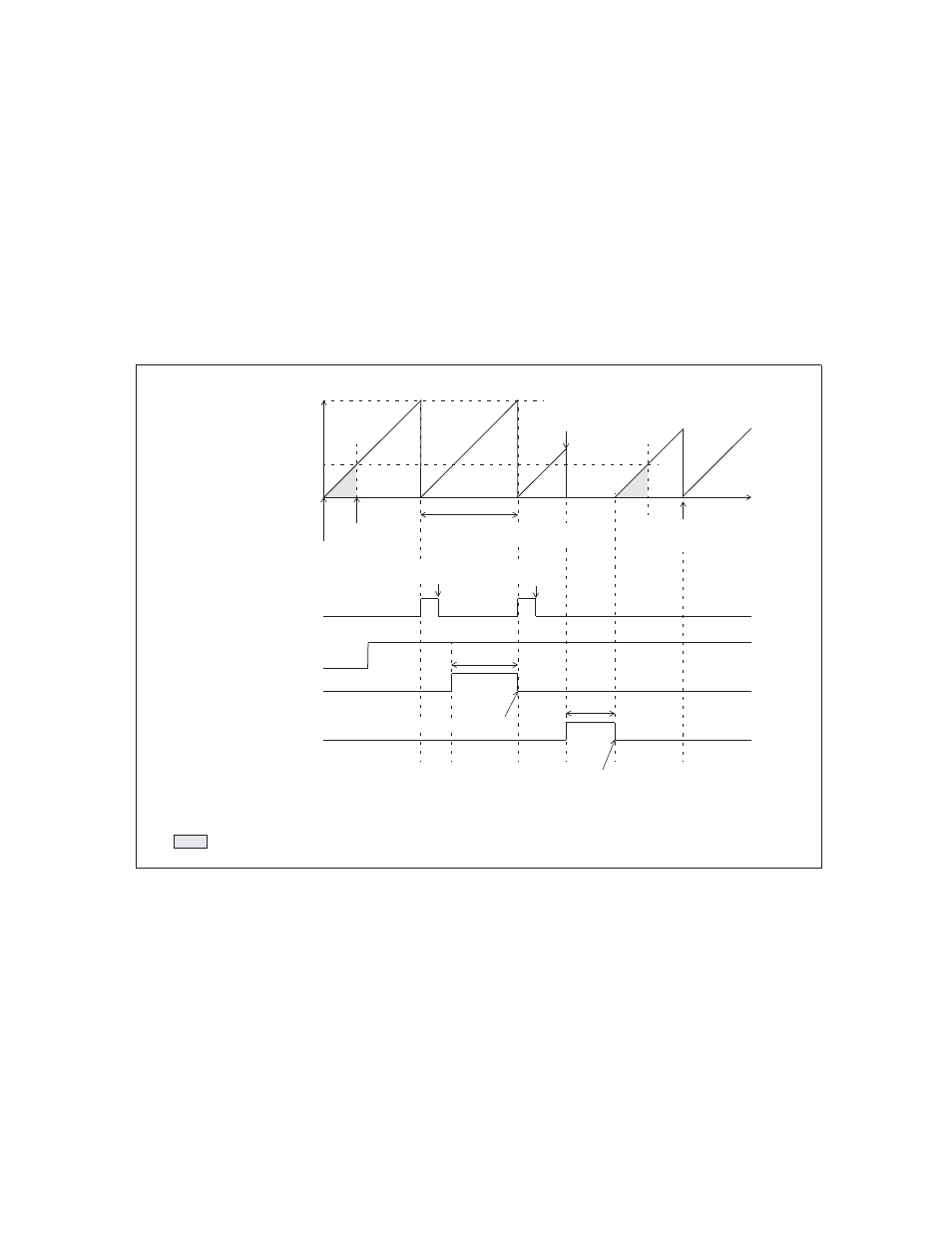

The state of following operations are shown in Figure 5.5-2 "Operation of timebase timer".

•

A power-on reset occurs.

•

Goes to sleep mode during operation of the interval timer function in the main clock mode.

•

Goes to stop mode.

•

A counter clear request occurs.

The timebase timer is cleared by going to stop mode, and its operation is stopped. The timebase timer

counts the oscillation stabilization delay time after wake-up from stop mode.

Figure 5.5-2 Operation of timebase timer

Counter value

1FFFFF

H

Oscillation stabilization

delay overflow

0000

H

Power-on reset

(optional)

CPU operation starts

Interval cycle

(TBTC: TBC1, TBC0 = “11

B

”)

Cleared by the interrupt

processing

routine.

Cleared by going to

stop mode.

Counter clear

(TBTC: TBR = “0”)

TBIF bit

TBIE bit

SLP bit

(STBC register)

STP bit

(STBC register)

Sleep mode

Wake-up from sleep mode

by IRQ6

Stop mode

Wake-up from stop mode by an external interrupt

: Indicates the oscillation stabilization delay time.

For the case when the interval time selection bits in the timebase timer control register

(TBTC: TBC1, TBC0) are set to "11

B

" (2

21

/F

CH

).