Lan leds, Boot process leds, Lan leds boot process leds – HP BL860C User Manual

Page 94: Table 20

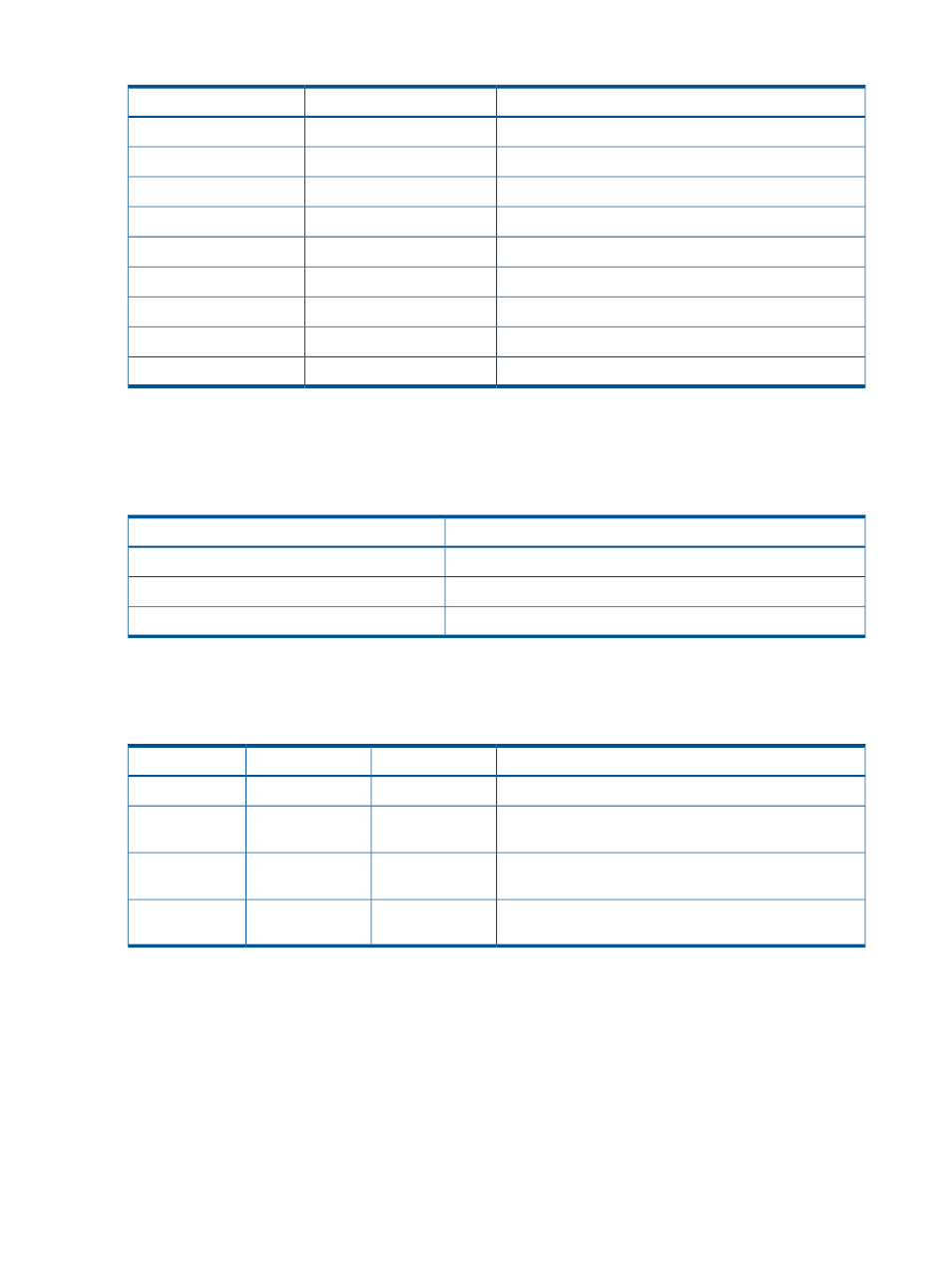

Table 20 SAS Disk Drive LEDs

SAS Disk Drive State

Status LED

Activity LED

Offline or not configured

Off

Off

Normal operation; no disk activity

Off

Solid green

Normal operation; disk read or write activity

Off

Flickering green

Offline, no disk activity; predictive failure

Flashing amber - 1/sec

Off

Online, no disk activity; predictive failure

Flashing amber - 1/sec

Solid green

Disk activity; predictive failure

Flashing amber - 1/sec

Flickering green

Offline; no disk activity; critical fault

Solid amber

Off

Offline; drive selected by locator function

Solid blue

Off

Drive rebuilding

Off

Flashing green - 1/sec

LAN LEDs

There are four LAN LEDs on the front panel of the server blade. They are NIC 1 through NIC 4.

details the functions of the LAN LEDs.

Table 21 1 GB LAN States

State

LED Color

No link

Off

Link found

Steady Green

LAN activity on network link

Flashing Green

Boot Process LEDs

shows the normal boot process, as reflected in changes to front panel LED states:

Table 22 Normal Boot Process LED States

Normal Power-Up Through HP-UX Boot

Power

Health

Step

No AC power to the server blade.

Off

Off

1

Server blade is shut down (server is off), AC power and

standby power is active, last health status was healthy.

Amber

Off

2

Server blade power rails are on when Power switch is

toggled. Hardware drives power LED.

Steady Green

Off

3

Server blade has powered up and is either at EFI, booting,

or at OS.

Steady green

Steady green

4

The following list itemizes the steps that characterize basic platform boot flow:

1.

Server blade power switch requests power from the Management Module (the microcontroller

that manages the enclosure power and cooling). Once the power is request is granted, server

blade power turns on. After the power sequence has completed successfully, BMC releases

system reset.

2.

Initial processor firmware code fetch is Platform Abstraction Layer (PAL) code from FEPROM

in processor-dependent hardware (PDH), retrieved 4 bytes at a time by the data

multiplexer/demultiplexer controller (DMDC) in zx1. No shared memory or I/O devices are

available at this time. They are not initially configured.

3.

Firmware code stack is initially in battery-backed RAM (BBRAM) in PDH, retrieved 4 byes at

a time, through the PDH and DMD buses.

94

Troubleshooting