Parallel interface signals behaviour – Compuprint 10200 Programmer Manual User Manual

Page 216

Interfaces

212

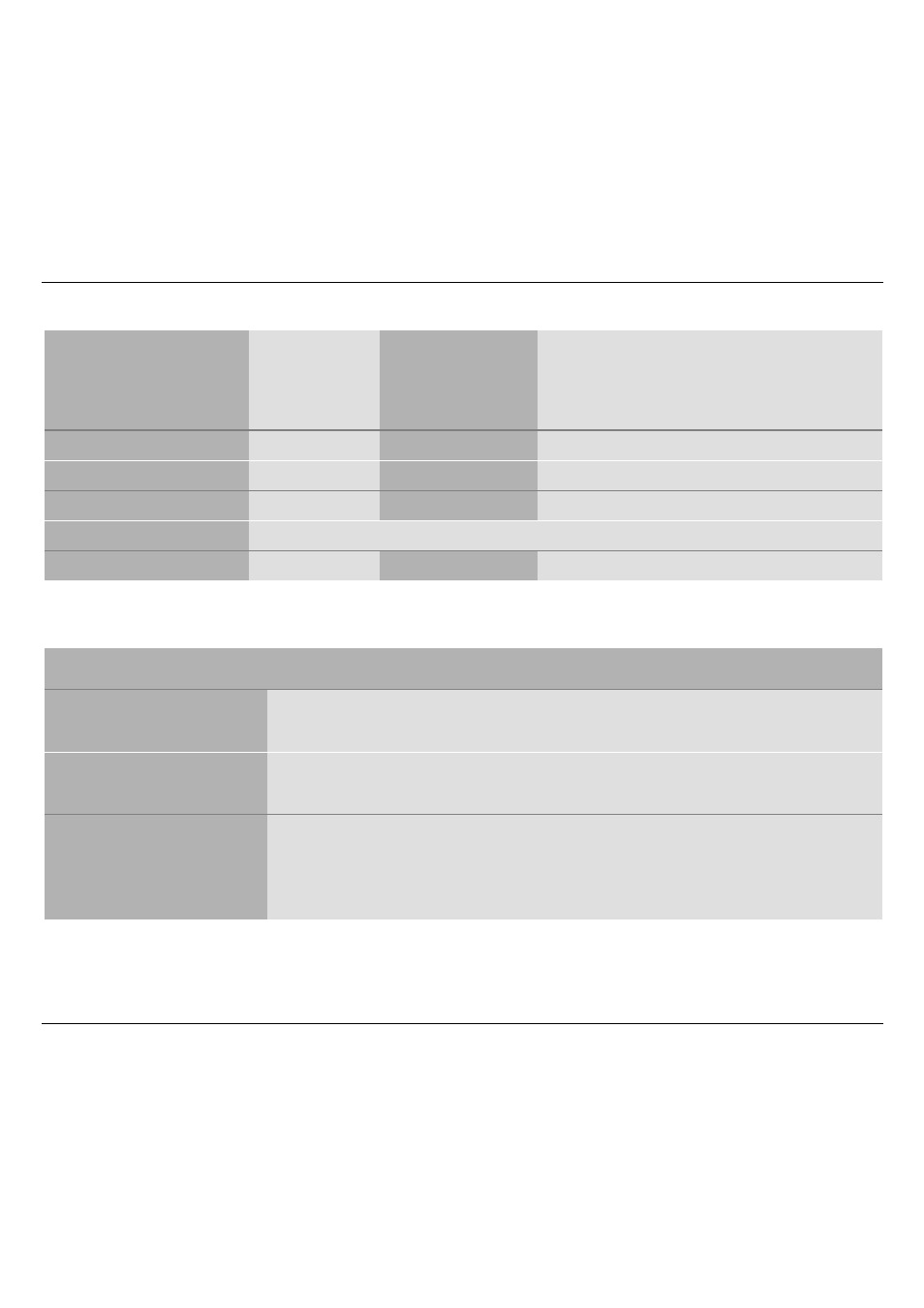

Signal Name

Pin N°

for Signal Wire

Pin N°

for Return Wire

Source

Peripheral Logic High (+

5V)

18

PRINTER

n.a. (nInit)

31

30

HOST

nDataAvail (NFault)

32

29

PRINTER

1284 Active (NSelectIn)

36

30

Common Logic Ground

16 and Return Wires

Chassis Ground

17

P

P

a

a

r

r

a

a

l

l

l

l

e

e

l

l

I

I

n

n

t

t

e

e

r

r

f

f

a

a

c

c

e

e

S

S

i

i

g

g

n

n

a

a

l

l

s

s

B

B

e

e

h

h

a

a

v

v

i

i

o

o

u

u

r

r

HostClk /nWrite (nStrobe)

Compatibility Mode:

Set Active low to transfer data into printer input latch. Data is valid while

nStrobe is low.

Negotiation Phase:

Set active low to transfer extendibility request value into printer input latch.

Data is valid on the falling edge of HostClk.

Reverse Data Transfer

Phase:

Set high during Nibble Mode transfer to avoid latching data into printer.

Pulsed low during Byte Mode transfers to acknowledge transfer of data from

the printer. The printer shall ensure that this pulse does not transfer a new

data into the printer input latch.