Synchronous flash, Synchronous flash –51 – Altera Arria V SoC Development Board User Manual

Page 59

Chapter 2: Board Components

2–51

Memory

July 2014

Altera Corporation

Reference Manual

Synchronous Flash

The development board supports a 512-Mb CFI-compatible synchronous flash device

for non-volatile storage of FPGA configuration data, board information, and test

application data. This device connects to the MAX V CPLD 5M2210 System Controller

for FPGA configuration in FPP and PS modes.

This 16-bit data memory interface can sustain burst read operations at up to 52 MHz

for a throughput of 832 Mbps per device. The write performance is 270 µs for a single

word buffer while the erase time is 800 ms for a 128 K array block.

lists the flash pin assignments, signal names, and functions. The signal

names and types are relative to the MAX V CPLD 5M2210 System Controller in terms

of I/O setting and direction.

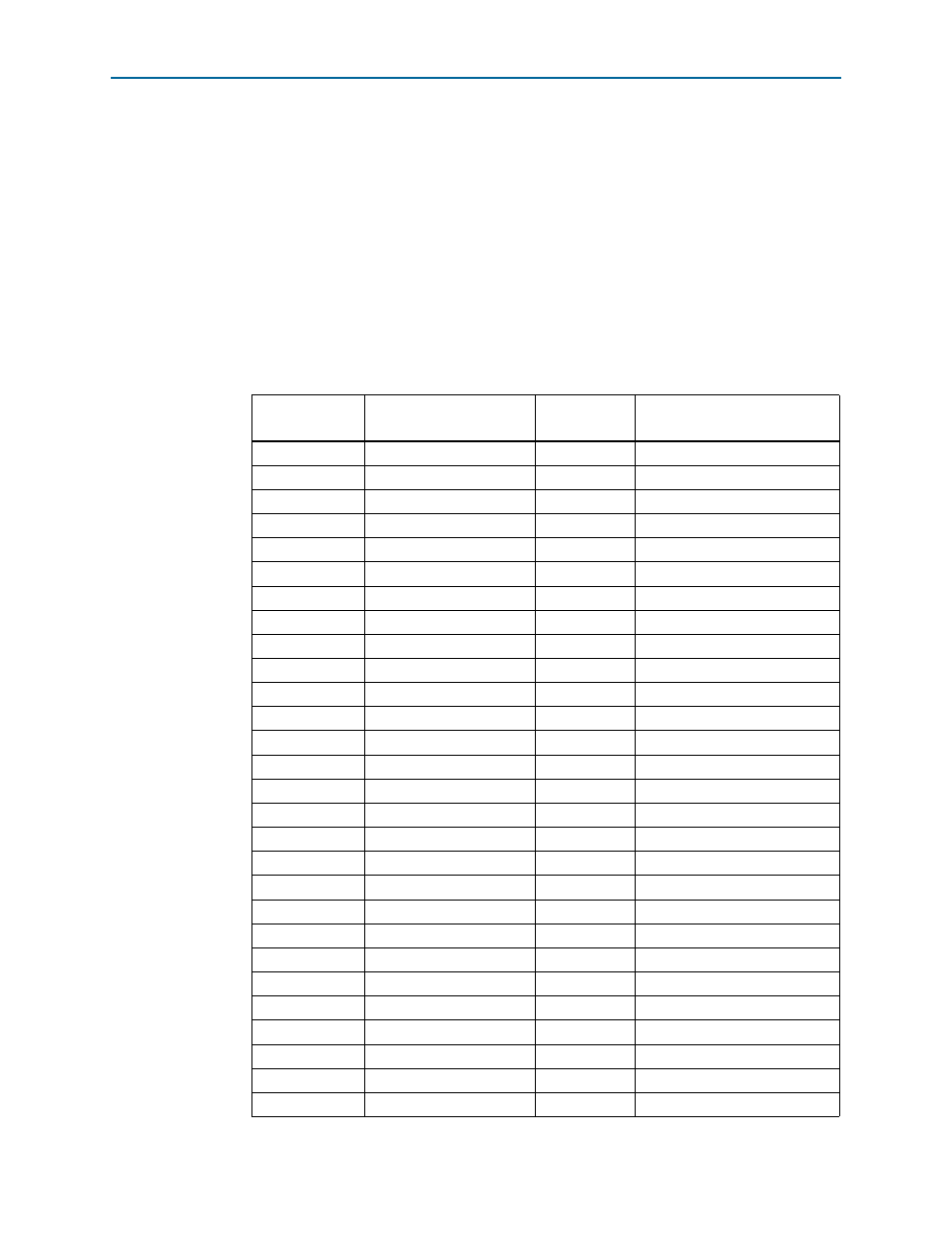

Table 2–31. Flash Pin Assignments, Schematic Signal Names, and Functions (Part 1 of 2)

Board

Reference (U13)

Schematic Signal Name

I/O Standard

Description

F6

FLASH_ADVN

1.8-V

Address valid

B4

FLASH_CEN0

1.8-V

Chip enable

E6

FLASH_CLK

1.8-V

Clock

F8

FLASH_OEN

1.8-V

Output enable

F7

FLASH_RDYBSYN

1.8-V

Ready

D4

FLASH_RESETN

1.8-V

Reset

G8

FLASH_WEN

1.8-V

Write enable

C6

FLASH_WPN

1.8-V

Write protect

A1

FSM_A1

1.8-V

Address bus

B1

FSM_A2

1.8-V

Address bus

C1

FSM_A3

1.8-V

Address bus

D1

FSM_A4

1.8-V

Address bus

D2

FSM_A5

1.8-V

Address bus

A2

FSM_A6

1.8-V

Address bus

C2

FSM_A7

1.8-V

Address bus

A3

FSM_A8

1.8-V

Address bus

B3

FSM_A9

1.8-V

Address bus

C3

FSM_A10

1.8-V

Address bus

D3

FSM_A11

1.8-V

Address bus

C4

FSM_A12

1.8-V

Address bus

A5

FSM_A13

1.8-V

Address bus

B5

FSM_A14

1.8-V

Address bus

C5

FSM_A15

1.8-V

Address bus

D7

FSM_A16

1.8-V

Address bus

D8

FSM_A17

1.8-V

Address bus

A7

FSM_A18

1.8-V

Address bus

B7

FSM_A19

1.8-V

Address bus

C7

FSM_A20

1.8-V

Address bus