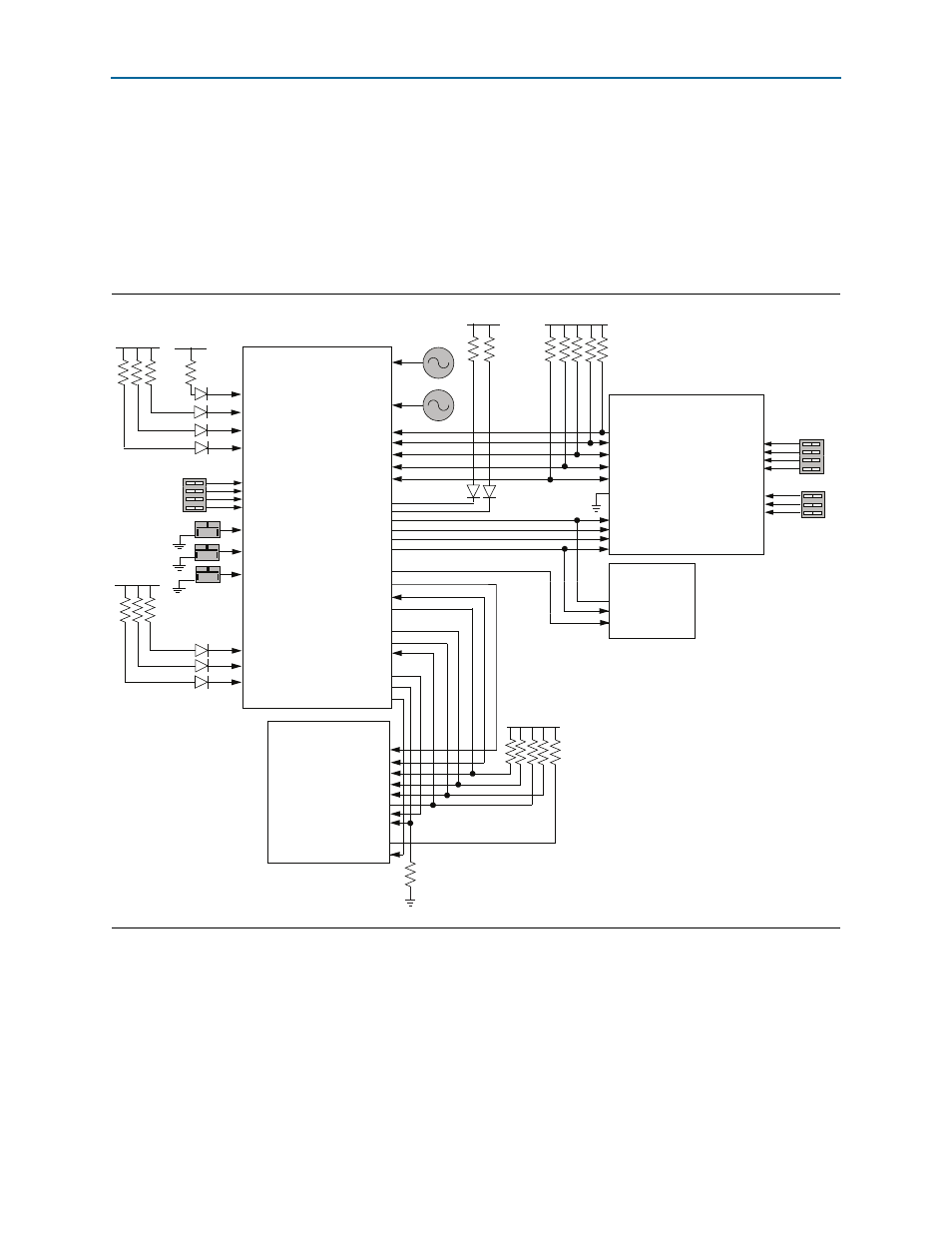

Figure 2–4. pfl configuration – Altera Arria V SoC Development Board User Manual

Page 22

2–14

Chapter 2: Board Components

FPGA Configuration

July 2014

Altera Corporation

Reference Manual

In AS configuration scheme, the data is read from the EPCQ flash and directly sent to

the FPGA. The MAX V CPLD 5M2210 System Controller controls the nCS line of the

EPCQ to avoid line contention on the data line due to functionality sharing. In order

to program non-volatile memory, CFI Flash or EPCQ special programming

functionality design should be loaded into the FPGA or MAX V CPLD to allow

programming using the Quartus II Programmer.

shows the PFL configuration.

f

For more information on the following topics, refer to the respective documents:

■

Board Update Portal, PFL design, and flash memory map storage, refer to the

■

PFL megafunction, refer to

Figure 2–4. PFL Configuration

MAX V CPLD

5M2210 System Controller

FPGA_DATA [3:0]

FPGA_DCLK

EPCQ_nCS

FLASH_A [25:1]

FLASH_D [15:0]

DATA [3:0]

DCLK

nSTATUS

nCONFIG

CONF_DONE

CONF_DONE

MSEL4

MSEL3

MSEL2

MSEL1

MSEL[4:0] and

BOOTSEL[3:0]

also connects to the

MAX V CPLD

2.5 V

10 k

Ω

nCE

DATA [3:0]

DCLK

nCE

CFI Flash

FLASH_CEn

FLASH_OEn

FLASH_WEn

FLASH_A [25:0]

FLASH_D [15:0]

FLASH_CEn

FLASH_OEn

FLASH_WEn

FLASH_WPn

FLASH_ADVn

FPGA_nCONFIG

FPGA_CONF_DONE

FLASH_RYBSYn

FLASH_RYBSYn

FPGA_nSTATUS

2.5 V

10 k

Ω

FLASH_ADVn

CVP_CONF_DONE

2.5 V

FLASH_CLK

FLASH_CLK

FLASH_RSTn

FLASH_RESETn

FPGA_DATA [4]

DATA [4]

FPGA_DATA [7:5]

DATA [7:5]

PS PORT

EPCQ

56.2

Ω

100

Ω

56.2

Ω

56.2

Ω

50 MHz

100 MHz

INIT_DONE

CVP_CONFDONE

FPGA_INIT_DONE

FPGA_CVP_DONE

2.5 V

2.5 V

2.5 V

MAX_ERROR

MAX_LOAD

FACTORY

USB_BLASTER

USB_SELECT

USER_PGM

CLK_ENABLE

CLK_SEL

CONFIG_RESETn

HPS_RESET

PGM_SEL

PGM_LED0

PGM_LED1

PGM_LED2

DIP Switch

BOOTSEL0

BOOTSEL1

BOOTSEL2

DIP Switch

DIP Switch

10 k

Ω

Arria V SoC FPGA