Hps jumpers, Cpu reset push button, Max v reset push button – Altera Arria V SoC Development Board User Manual

Page 26

2–18

Chapter 2: Board Components

Setup Elements

July 2014

Altera Corporation

Reference Manual

HPS Jumpers

The HPS jumpers define the bootstrap options for the HPS—boot source, mode, HPS

clocks settings, power-on-reset (POR) mode and peripherals selection.

lists

the jumper settings and its descriptions.

CPU Reset Push Button

The CPU reset push button,

CPU_RESETn

(S4), is an input to the Arria V HPS pin and is

an open-drain I/O from the MAX V CPLD System Controller. This push button is the

default reset for both the HPS and CPLD logic. The MAX V CPLD 5M2210 also drives

this push button during POR mode.

MAX V Reset Push Button

The MAX V reset push button,

MAX_RESETn

(S11), is an input to the MAX V CPLD

5M2210 System Controller. This push button is the default reset for the CPLD logic.

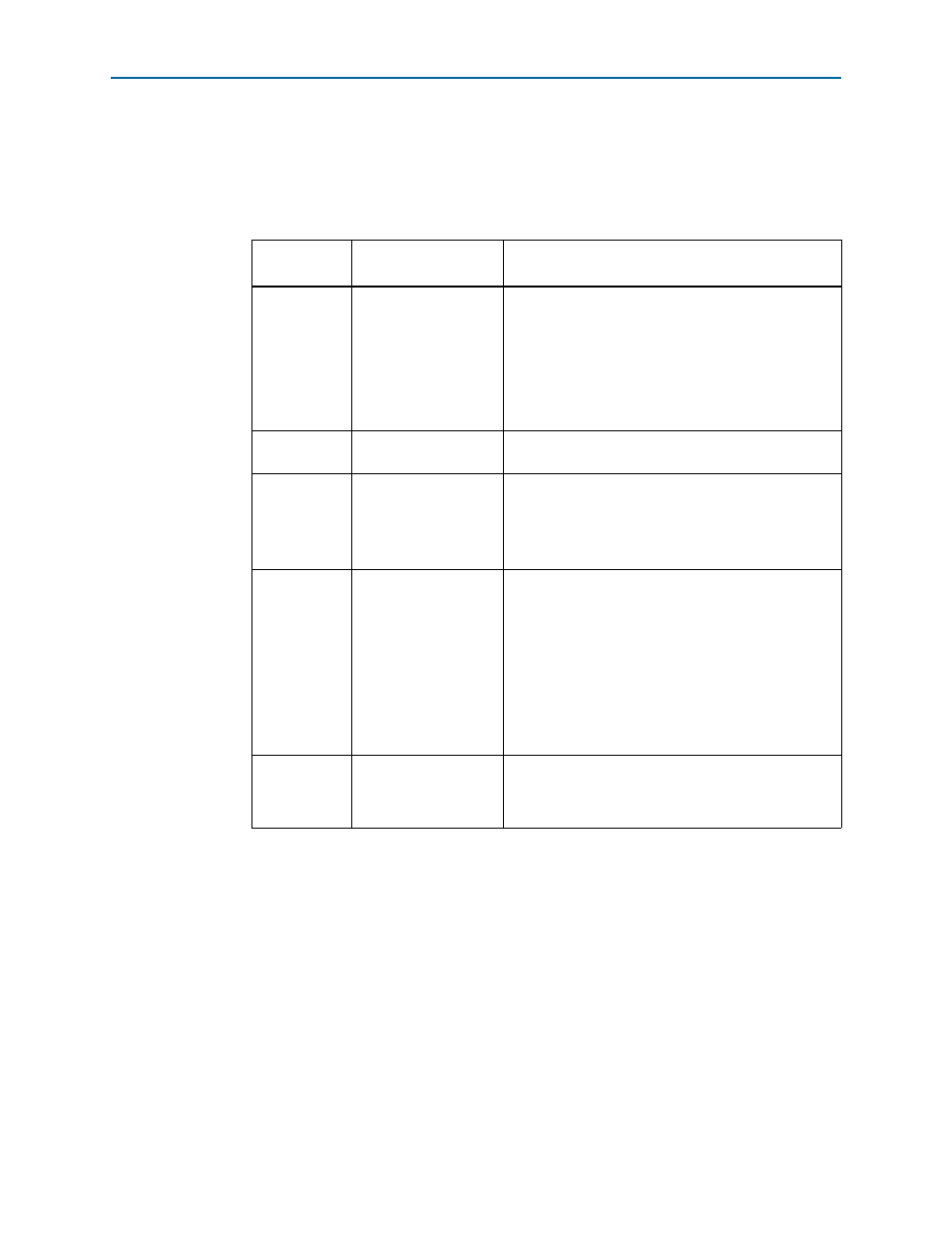

Table 2–10. HPS Jumpers

Board

Reference

Schematic Signal

Name

Description

J39, J40, J41

HPS_BSEL[2:0]

Selects the boot mode and source for the HPS.

■

0x1—FPGA

■

0x3—NAND flash (not supported on this board)

■

0x5—Micro SD card

■

0x7—QSPI flash

All the other modes are reserved.

J37, J38

HPS_CSEL[1:0]

Selects the HPS clock settings. The actual clock settings

are also dependent on the HPS_BSEL[2:0] selection.

J45, J46

OSC2_CLK_SEL[1:0]

Selects the source of OSC2 clock.

■

00—Select on-board clock generator.

■

01—Select external source via SMA connector.

■

10—Select 33 MHz on-board oscillator

J19

JTAG_HPS_SEL

HPS in JTAG chain or only connect HPS to MICTOR.

Selects the source to control the HPS.

■

ON: Select on-board USB-Blaster II as the JTAG

master.

■

OFF: Select MICTOR-based JTAG master, such as

DSTREAM or Lauterbach programming cables. Also,

sets SW4.1 to ON to remove the on-board USB

Blaster II from driving the HPS JTAG input port in this

mode.

J21

JTAG_SEL

Selects the source of the JTAG chain.

■

ON: Select on-board USB-Blaster II as the source.

■

OFF: Select MICTOR as the source.