Altera Stratix IV E FPGA Development Board User Manual

Page 54

2–46

Chapter 2: Board Components

Memory

Stratix IV E FPGA Development Board Reference Manual

May 2011

Altera Corporation

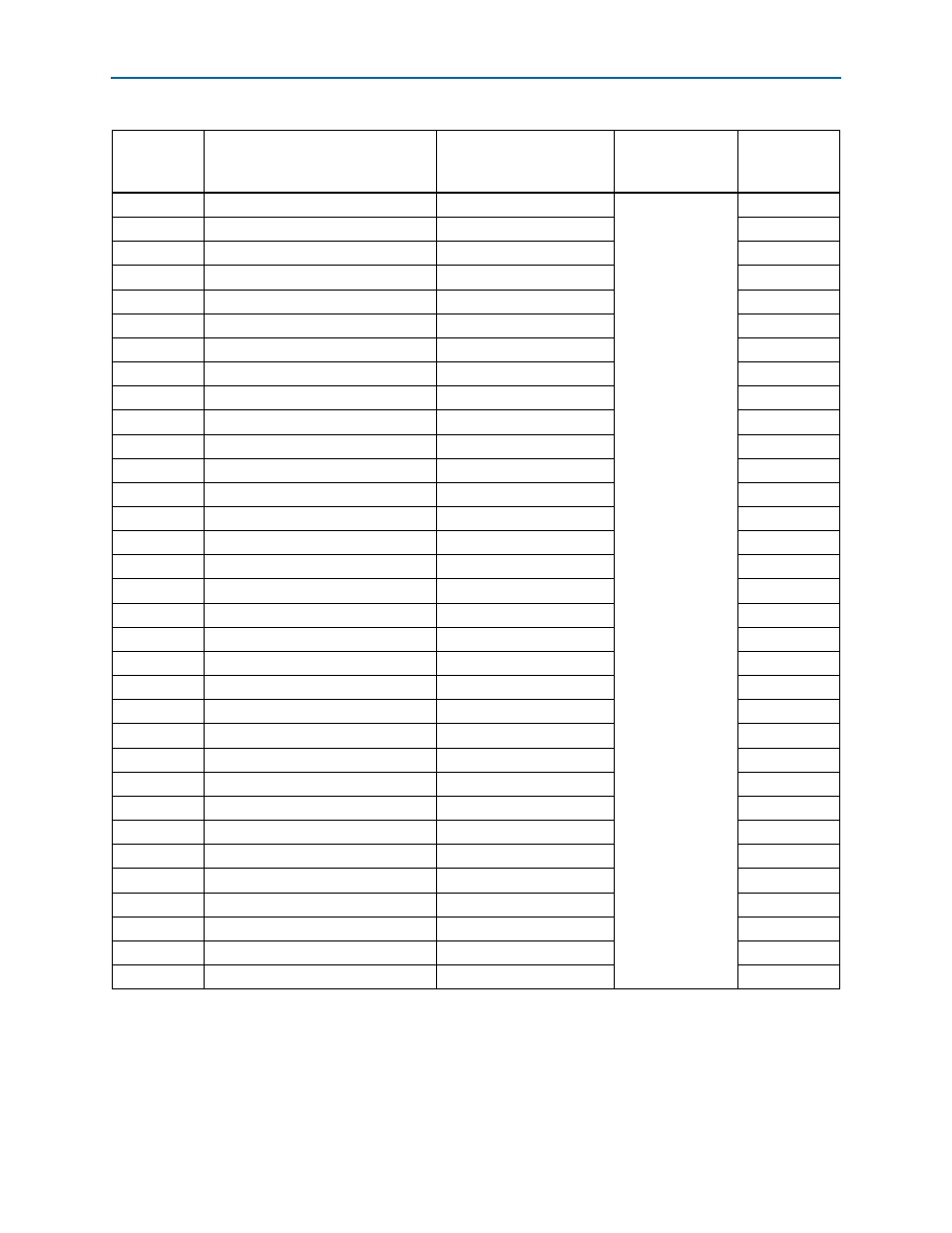

J20.126

Data strobe bit N9

DDR3_DIMM_DQS_N9

1.5-V SSTL Class I

AK28

J20.135

Data strobe bit N10

DDR3_DIMM_DQS_N10

AH24

J20.144

Data strobe bit N11

DDR3_DIMM_DQS_N11

AL27

J20.153

Data strobe bit N12

DDR3_DIMM_DQS_N12

AJ22

J20.204

Data strobe bit N13

DDR3_DIMM_DQS_N13

AL21

J20.213

Data strobe bit N14

DDR3_DIMM_DQS_N14

AP12

J20.222

Data strobe bit N15

DDR3_DIMM_DQS_N15

AL9

J20.231

Data strobe bit N16

DDR3_DIMM_DQS_N16

AM5

J20.162

Data strobe bit N17

DDR3_DIMM_DQS_N17

AG21

J20.7

Data strobe bit P0

DDR3_DIMM_DQS_P0

AM31

J20.16

Data strobe bit P1

DDR3_DIMM_DQS_P1

AN33

J20.25

Data strobe bit P2

DDR3_DIMM_DQS_P2

AN28

J20.34

Data strobe bit P3

DDR3_DIMM_DQS_P3

AL24

J20.85

Data strobe bit P4

DDR3_DIMM_DQS_P4

AN22

J20.94

Data strobe bit P5

DDR3_DIMM_DQS_P5

AH14

J20.103

Data strobe bit P6

DDR3_DIMM_DQS_P6

AH11

J20.112

Data strobe bit P7

DDR3_DIMM_DQS_P7

AN3

J20.43

Data strobe bit P8

DDR3_DIMM_DQS_P8

AN25

J20.53

DIMM error output

DDR3_DIMM_ERR_OUTn

AG19

J20.187

DIMM event

DDR3_DIMM_EVENTn

AE11

J20.195

On-die termination control pin 0

DDR3_DIMM_ODT0

AL14

J20.77

On-die termination control pin 1

DDR3_DIMM_ODT1

AL13

J20.68

DIMM parity input

DDR3_DIMM_PAR_IN

AH19

J20.192

Row address strobe

DDR3_DIMM_RASn

AL15

J20.168

Reset

DDR3_DIMM_RESETn

AJ19

J20.118

Presence detect clock input

DDR3_DIMM_SCL

AF20

J20.238

Presence detect data

DDR3_DIMM_SDA

AN19

—

Test pin

DDR3_DIMM_TEST1

AC22

—

Test pin

DDR3_DIMM_TEST2

AE24

—

Test pin

DDR3_DIMM_TEST3

AF19

—

Test pin

DDR3_DIMM_TEST4

AF11

—

Test pin

DDR3_DIMM_TEST5

AC12

J20.73

Write enable

DDR3_DIMM_WEn

AM14

Table 2–43. DDR3 Pin Assignments, Schematic Signal Names, and Functions (Part 5 of 5)

Board

Reference

Description

Schematic Signal Name

I/O Standard

Stratix IV E

Device

Pin Number