Altera Stratix IV E FPGA Development Board User Manual

Page 40

2–32

Chapter 2: Board Components

Components and Interfaces

Stratix IV E FPGA Development Board Reference Manual

May 2011

Altera Corporation

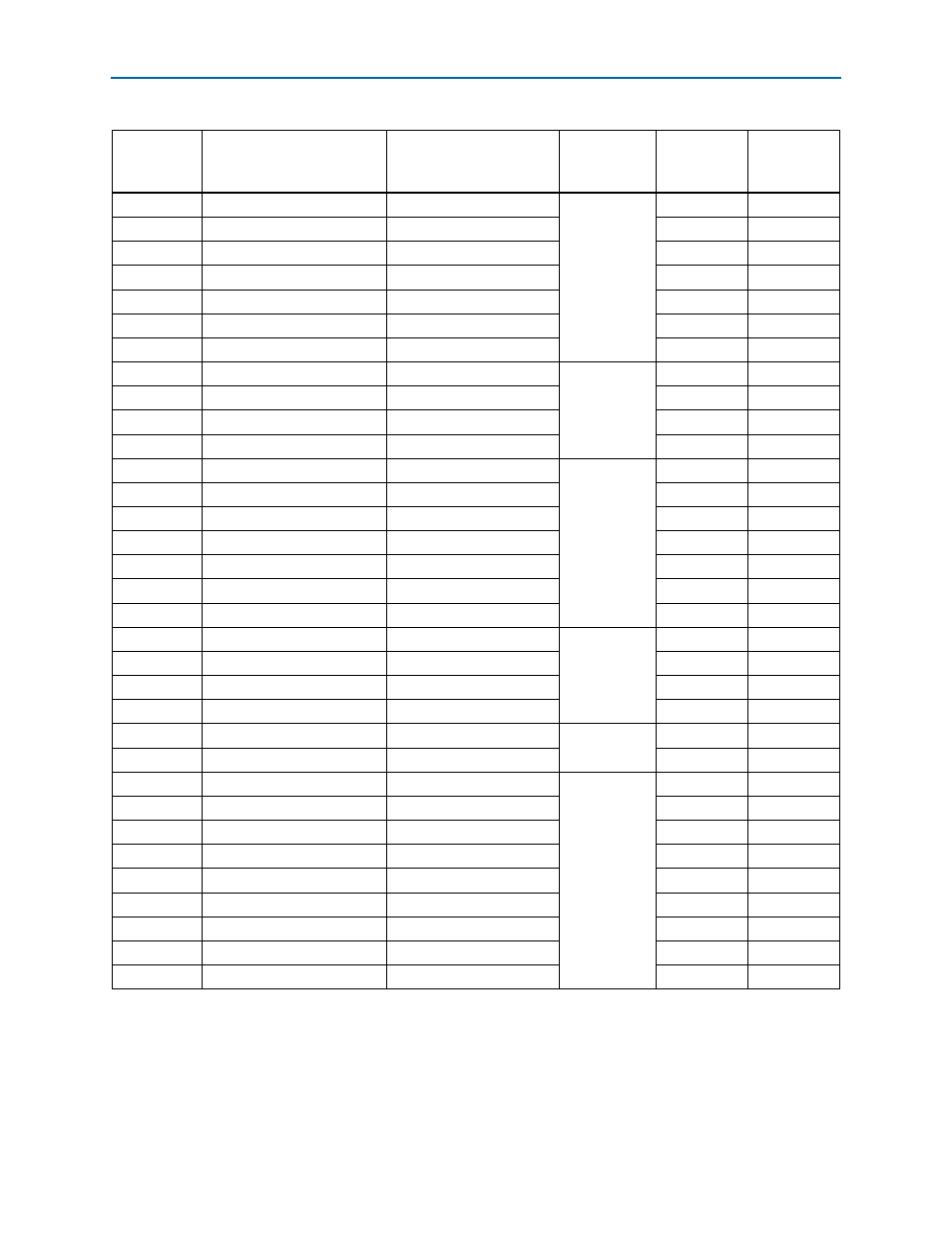

U15.91

RSGMII receive data bus

ENET_RX_D3

2.5-V

M34

—

U15.90

RSGMII receive data bus

ENET_RX_D4

C34

—

U15.89

RSGMII receive data bus

ENET_RX_D5

P29

—

U15.87

RSGMII receive data bus

ENET_RX_D6

H34

—

U15.86

RSGMII receive data bus

ENET_RX_D7

J32

—

U15.94

RSGMII receive control

ENET_RX_DV

P32

—

U15.3

GMII receive error

ENET_RX_ER

K31

—

U15.75

SGMII receive data

ENET_RX_N

LVDS

D34

—

U15.77

SGMII receive data

ENET_RX_P

D33

—

U15.80

SGMII 625 MHz Clock

ENET_S_CLKN

V32

—

U15.79

SGMII 625 MHz Clock

ENET_S_CLKP

V31

—

U15.4

25 MHz MII Transmit Clock

ENET_TX_CLK

2.5-V

R32

—

U15.11

RGMII transmit data bus

ENET_TX_D0

P28

—

U15.12

RGMII transmit data bus

ENET_TX_D1

F34

—

U15.14

RGMII transmit data bus

ENET_TX_D2

N34

—

U15.16

RGMII transmit data bus

ENET_TX_D3

L28

—

U15.17

RGMII transmit data bus

ENET_TX_D4

G33

—

U15.18

RGMII transmit data bus

ENET_TX_D5

C33

—

U15.19

RGMII transmit data bus

ENET_TX_D6

2.5-V

N33

—

U15.20

RGMII transmit data bus

ENET_TX_D7

G31

—

U15.9

RGMII transmit control

ENET_TX_EN

L34

—

U15.7

GMII transmit error

ENET_TX_ER

M29

—

U15.81

SGMII data input

ENET_TX_N

LVDS

T30

—

U15.82

SGMII data input

ENET_TX_P

T29

—

U15.55

25 MHz crystal

ENET_XTAL_25MHZ

2.5-V

—

X1.4

U15.31

Media dependent interface

MDI_N0

—

J8.2

U15.34

Media dependent interface

MDI_N1

—

J8.6

U15.41

Media dependent interface

MDI_N2

—

J8.5

U15.43

Media dependent interface

MDI_N3

—

J8.8

U15.29

Media dependent interface

MDI_P0

—

J8.1

U15.33

Media dependent interface

MDI_P1

—

J8.3

U15.39

Media dependent interface

MDI_P2

—

J8.4

U15.42

Media dependent interface

MDI_P3

—

J8.7

Table 2–37. Ethernet PHY Pin Assignments, Signal Names and Functions

Board

Reference

Description

Schematic Signal Name

I/O Standard

Stratix IV E

Device

Pin Number

Other

Connections