I/o resources, I/o resources –6 – Altera Stratix IV E FPGA Development Board User Manual

Page 14

2–6

Chapter 2: Board Components

Featured Device: Stratix IV E Device

Stratix IV E FPGA Development Board Reference Manual

May 2011

Altera Corporation

I/O Resources

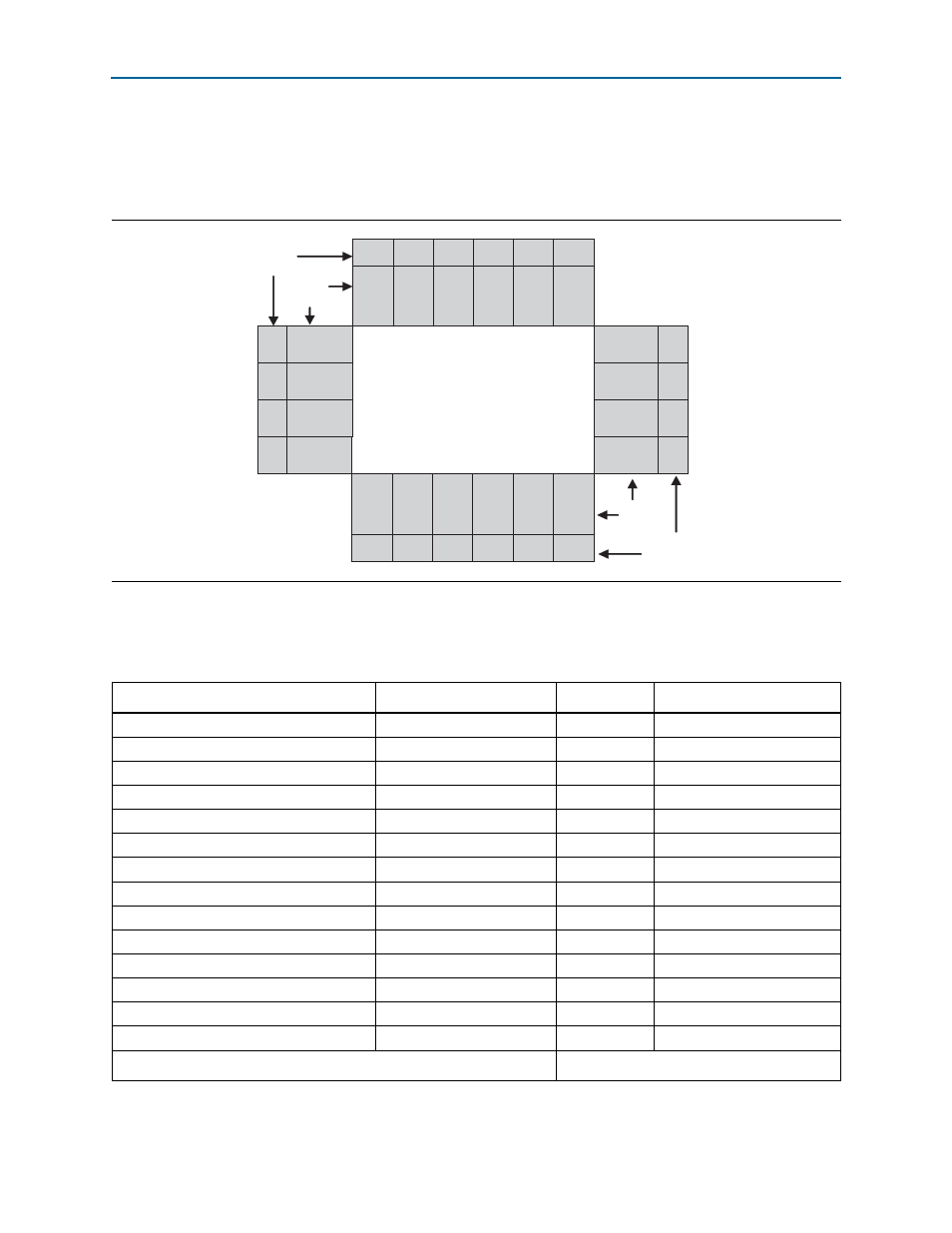

illustrates the bank organization and I/O count for the EP4SE530 device in

the 1152-pin FBGA package.

lists the Stratix IV E device pin count and usage by function on the

development board.

Figure 2–2. EP4SE530 Device I/O Bank Diagram

EP4SE290

EP4SE360

EP4SE530

EP4SE680

B

ank

8B

24

B

ank

7A

40

B

ank

7B

24

B

ank

7C

32

40 Bank 1C

40 Bank 2C

24

B

ank

3B

40

B

ank

4A

24

B

ank

4B

32

B

ank

4C

Bank 6C 40

Bank 5C 40

48

Bank 2A

B

ank

8C

32

B

ank

8A

40

32

B

ank

3C

40

B

ank

3A

Bank 5A

48

Bank 6A

48

Bank

Name

Number

of I/Os

Bank

Name

Number

of I/Os

48

Bank 1A

Table 2–4. Stratix IV E Device Pin Count and Usage

Function

I/O Standard

I/O Count

Special Pins

OSC/SMAs

1.5-V/2.5-V CMOS

13

12 Clock Inputs, 1 Output

DDR3 DIMM

1.5-V SSTL

153

18 DQS pins

QDR II+

1.5-V HSTL

69

2 CQ pins

RLDRAM II CIO

1.5-V HSTL

77

—

HSMC Port A

2.5-V CMOS + LVDS

86

3 Clock Inputs

HSMC Port B

2.5-V CMOS + LVDS

86

3 Clock Inputs

Flash, SSRAM, MAX

2.5-V CMOS

91

—

Gigabit Ethernet

2.5-V CMOS

36

—

User I/O (LEDs, DIP Switch, Push-Buttons)

1.5-V/2.5-V CMOS

21

—

14-pin LCD Header

2.5-V CMOS

11

—

Graphic Display

2.5-V CMOS

15

—

Seven-Segment Display

2.5-V CMOS

13

—

EEPROM

2.5-V CMOS

4

—

MAX II Control, Speaker

2.5-V CMOS

6

—

Device I/O Total:

681