Tables 1–4 – Altera QDRII SRAM Controller MegaCore Function User Manual

Page 9

Altera Corporation

MegaCore Version 9.1

1–5

November 2009

QDRII SRAM Controller MegaCore Function User Guide

About This MegaCore Function

1

These numbers apply to both commercial and industrial

devices.

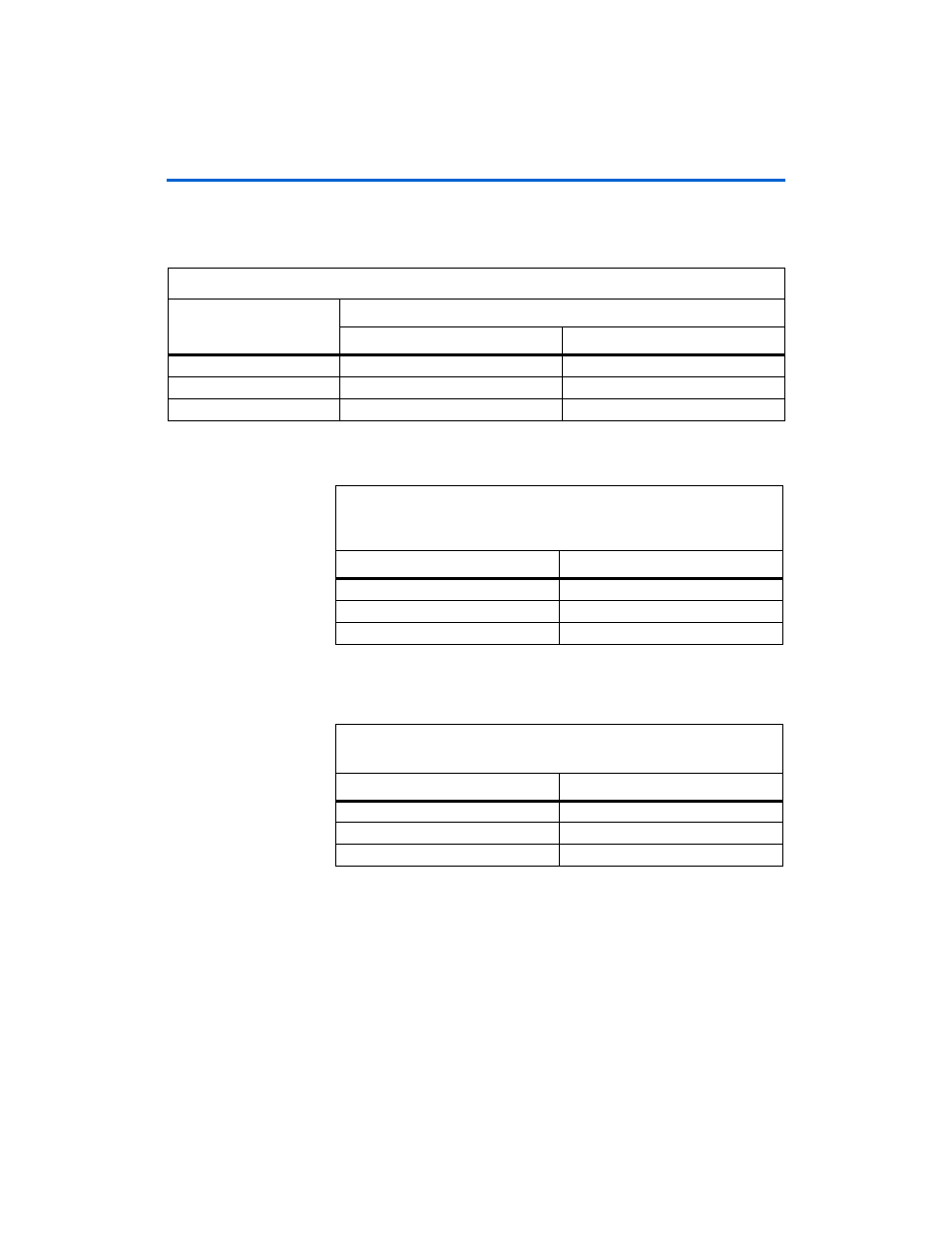

Table 1–4. QDRII SDRAM Maximum Clock Frequency Support in Stratix II & Stratix II GX Devices

Speed Grade

Frequency (MHz)

DLL-Based Implementation

PLL-Based Implementation

–3

300

200

–4

200

167

–5

200

167

Notes to

:

(1)

This analysis is based on the EP2S90F1020 device. Ensure you perform a timing analysis for your chosen FPGA.

Table 1–5. QDRII SRAM Maximum Clock Frequency Supported in Stratix &

Stratix GX Devices (EP1S10 to EP1S40 & EP1SGX10 to EP1SGX40 Devices)

Speed Grade

Frequency (MHz)

–5

200

–6

167

–7

133

(1)

This analysis is based on the EP1S25F1020 device. Ensure you perform a timing

analysis for your chosen FPGA.

Table 1–6. QDRII SRAM Maximum Clock Frequency Supported in Stratix

Devices (EP1S60 to EP1S80 Devices)

Speed Grade

Frequency (MHz)

–5

167

–6

167

–7

133

(1)

This analysis is based on the EP1S60F1020 device. Ensure you perform a timing

analysis for your chosen FPGA.