Altera QDRII SRAM Controller MegaCore Function User Manual

Page 60

3–28

MegaCore Version 9.1

Altera Corporation

QDRII SRAM Controller MegaCore Function User Guide

November 2009

Device-Level Configuration

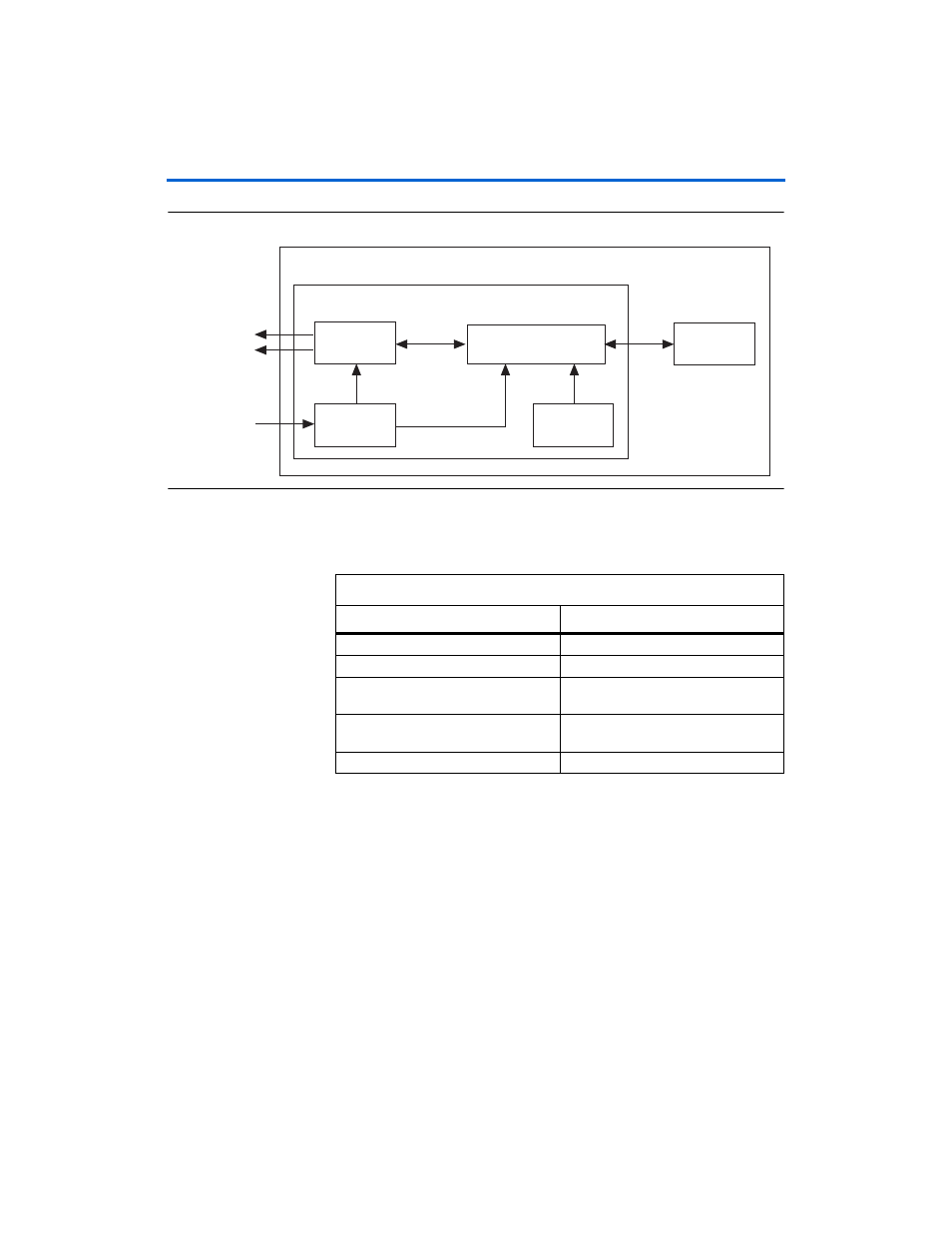

Figure 3–21. Testbench & Example Design

describes the files that are associated with the example design

and the testbench.

The example driver is a self-checking test generator for the QDRII SRAM

controller. It uses a state machine to write data patterns to all memory

banks. It then reads back the data and checks that the data matches. If any

read data fails the comparison, the fail output transitions high for one

cycle and the fail permanent output transitions high and stays high.

The data patterns used are generated using an 8-bit counter per byte, with

each counter having a different initialization seed.

Example Driver

PLL

ref_clk

test_complete

pnf

Example Design

Testbench

QDRII SRAM Controller

QDRII SRAM

Model

DLL

Table 3–7. Example Design & Testbench Files

Filename

Description

<top-level name>_tb.v or .vhd

Testbench for the example design.

<top-level name>.vhd or .v

Example design.

qdrii_pll_stratixii.vhd

Example PLL, which you should

configure to match your frequency.

<variation name>_example_driver.v

or .vhd

Example driver.

<variation name> .v or .vhd

QDRII SRAM controller.

(1)

<top-level name> is the name of the Quartus II project top-level entity.

(2)

<variation name> is the is the name you give to the controller you create with the

Megawizard.