Simultaneous read & write timing, Burst of four (narrow mode) – Altera QDRII SRAM Controller MegaCore Function User Manual

Page 51

Altera Corporation

MegaCore Version 9.1

3–19

November 2009

QDRII SRAM Controller MegaCore Function User Guide

Functional Description

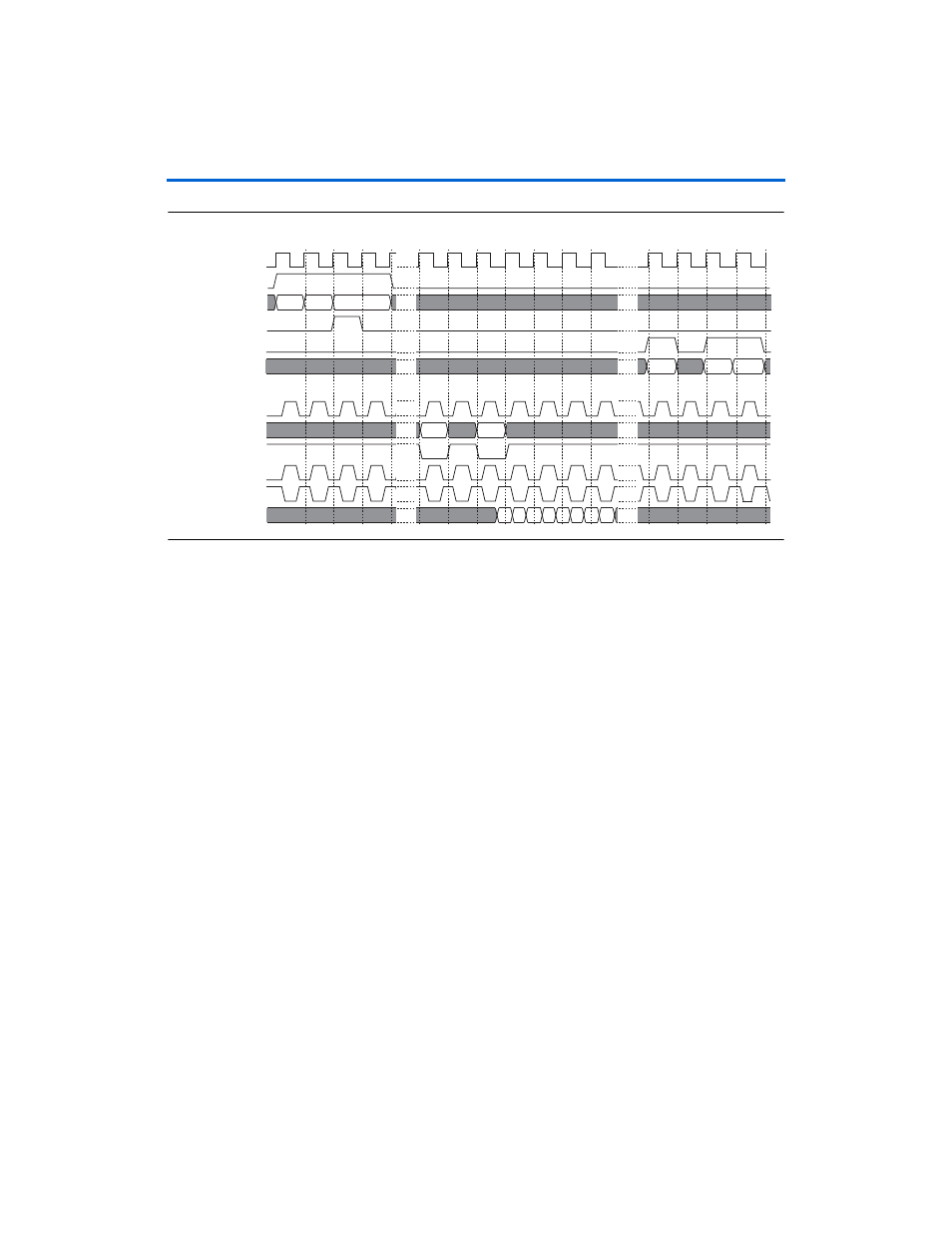

Figure 3–16. Burst with Non-Consecutive Address—Burst of Four (Narrow Mode)

Simultaneous Read & Write Timing

This section discusses the following topics:

■

“Burst of Four (Narrow Mode)” on page 3–19

■

■

“Burst of Four (Wide Mode)” on page 3–21

The QDRII SRAM protocol allows simultaneous reads and writes to the

memory. As the address bus is shared between the read and write, if a

concurrent read and write occurs, some arbitration may be necessary.

Burst of Four (Narrow Mode)

For a burst of four, you cannot send a read and a write request during the

same clock cycle. Because it takes two clock cycle per transfer, you can

alternate reads and writes every other cycle. Thus you lose no bandwidth

apart from an initial one clock cycle on either the read or the write.

When a read and a write arrive at the same time, the write takes priority

over the read. For a continuous read and write, there is a one off pause on

the read side, refer to

.

avl_clk

avl_read

avl_data_rd[19:0]

avl_wait_request_rd

avl_data_read_valid

avl_data_rd[17:0]

qdrii_k

qdrii_a[19:0]

qdrii_rpsn

qdrii_cq

qdrii_cqn

qdrii_q[17:0]

0001 1220

1221

0102

3132

3334

3334

0001

1220

01 02 xx xx 31 32 33 34

34