Writes, Isolated write – Altera QDRII SRAM Controller MegaCore Function User Manual

Page 43

Altera Corporation

MegaCore Version 9.1

3–11

November 2009

QDRII SRAM Controller MegaCore Function User Guide

Functional Description

■

■

■

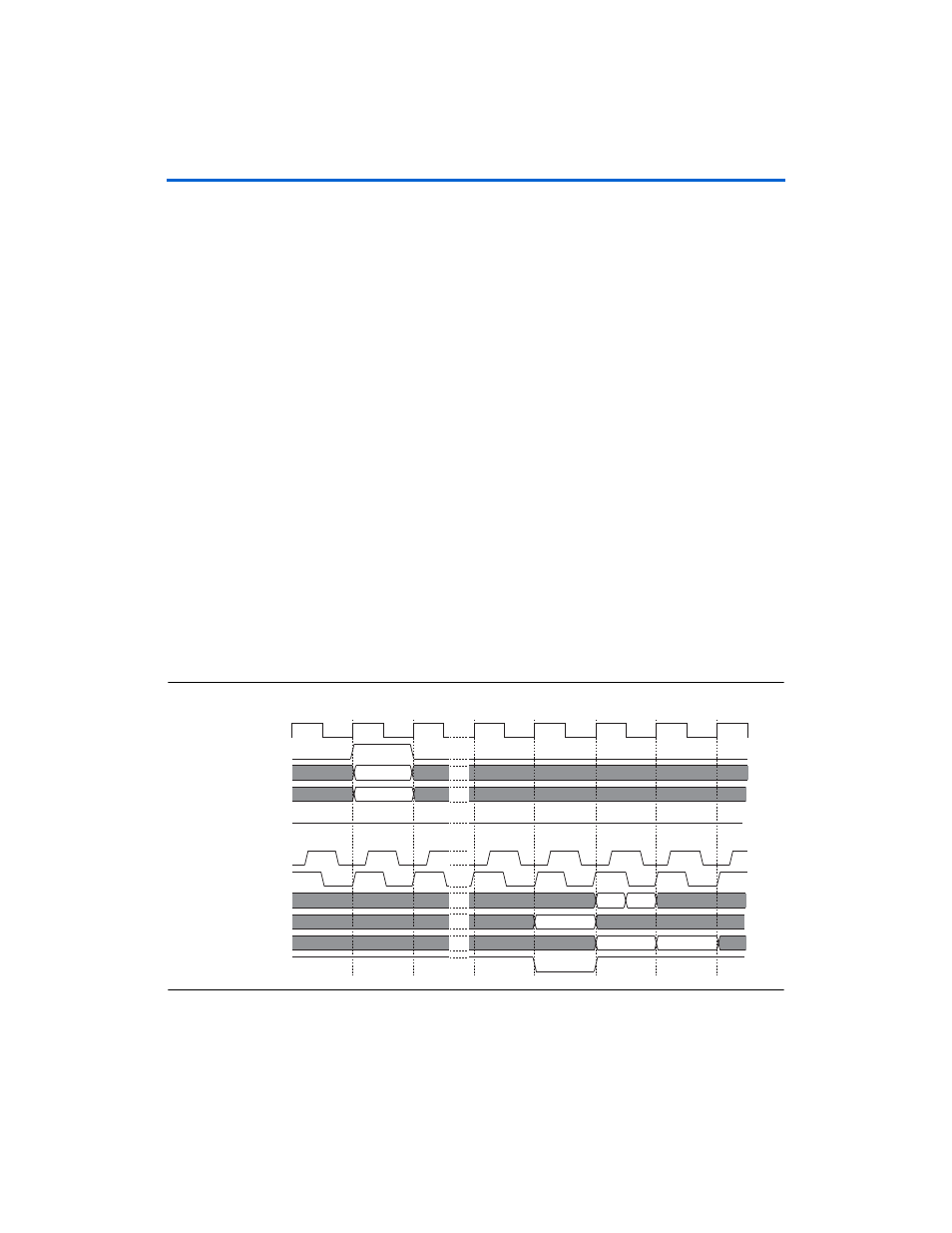

Simultaneous Read & Write Timing

f

For more information on the Avalon interface, refer to

.

Writes

This section discusses the following topics:

■

■

■

“Bursts with Pauses” on page 3–14

If the address is the consecutive, you can have consecutive write cycles

(refer to

). Non-consecutive addresses are split

into two transfers and you must pause a transfer (refer to

).

Isolated Write

shows an isolated write transaction on a burst of four (narrow

mode). The Avalon interface receives a write request, which the

controller immediately accepts. It then transfers the write data (the exact

timing may vary) to the QDRII SRAM interface. As it receives only half

the required data for a burst of four, it masks the second part of the burst

on the QDRII SRAM interface as invalid.

Figure 3–7. Isolated Write—Burst of Four (Narrow Mode)

clk

avl_write

avl_data_wr[35:0]

avl_adr_wr[19:0]

avl_wait_request_wr

write_clk

system_clk

qdrii_d[17:0]

qdrii_a[19:0]

qdrii_bwsn[1:0]

qdrii_wpsn

00010002

00010002

0001

0001

0001

0002

0002

0001

0001

00

11

11