Altera QDRII SRAM Controller MegaCore Function User Manual

Page 20

2–10

MegaCore Version 9.1

Altera Corporation

QDRII SRAM Controller MegaCore Function User Guide

November 2009

QDRII SRAM Controller Walkthrough

2.

After you review the generation report, click Exit to close IP

Toolbench.

You have finished the walkthrough. Now, simulate the example design

(refer to

“Simulate the Example Design” on page 2–11

), edit the PLL(s)

(refer to

), and compile (refer to

).

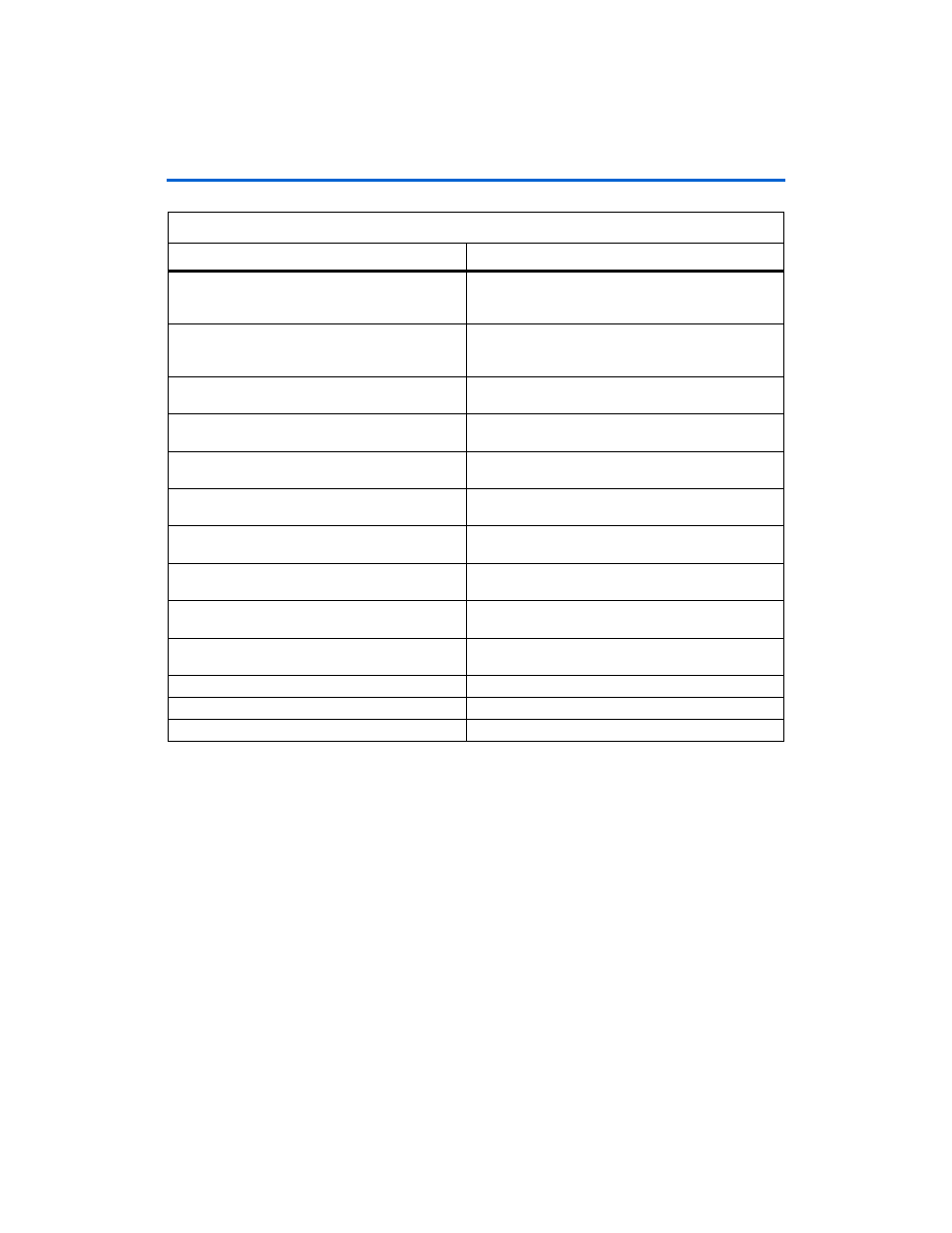

hd or .v

File that includes the write data pipeline and includes the

address and command, read command, write data, and

write command pipeline.

or .v

Address and command pipeline.

Read data pipeline.

Write data pipeline.

The read registers.

The resynchronization FIFO buffers.

File that contains all the training group modules.

Training module, which realigns latency.

The write registers.

<variation name>.qip

Contains Quartus II project information for your

MegaCore function variations.

Example design file.

add_constraints_for_

The add constraints script.

qdrii_pll_stratixii.vhd or .v

Stratix II PLL.

Notes to

:

(1)

<top-level name> is the name of the Quartus II project top-level entity.

(2)

<variation name> is the name you give to the controller you create with the Megawizard.

(3)

IP Tooblench replaces the string qdrii_sram with qdriiplus_sram for QDRII+ SRAM controllers.

Table 2–1. Generated Files (Part 2 of 2)

(1)

,

(2)

&

(3)

Filename

Description