Altera Internal Memory (RAM and ROM) IP Core User Manual

Page 49

Option

Value

How wide should the data be?

13 bits

Do you want to pipeline the functions?

Yes, I want an output latency of 1 clock cycle

Create an 'aclr' asynchronous clear port

Not selected

Create a 'clocken' clock enable clock

Not selected

8. Click Finish. The ecc_decoder.v module is built.

9. In the IP Catalog double-click the ALTECC IP core. The parameter editor appears.

10.Specify the following parameters:

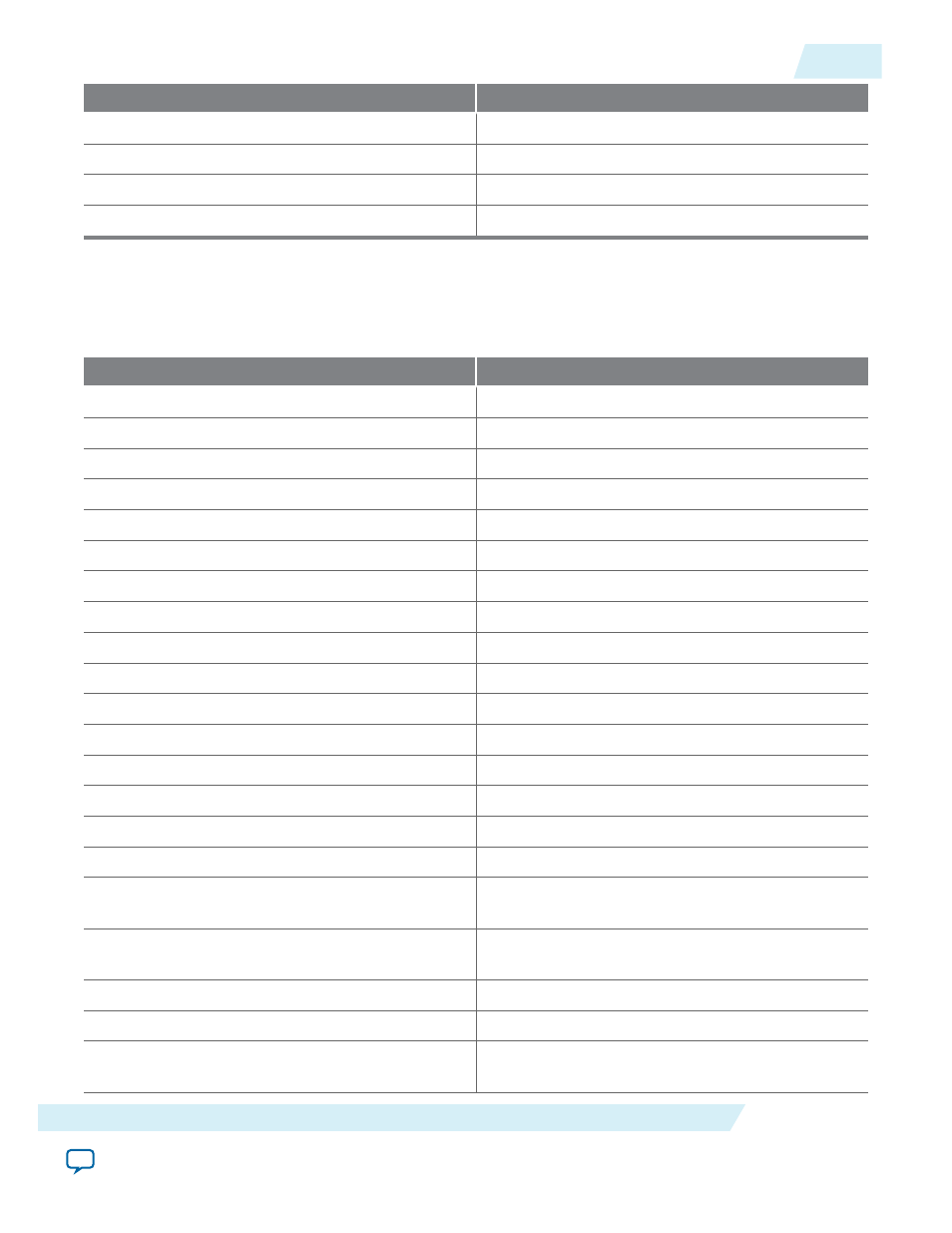

Table 5-3: Configuration Settings for RAM: 2-Port IP Core

Option

Value

Which type of output file do you want to create?

Verilog HDL

What name do you want for the output file?

true_dp_ram

Return to this page for another create operation

Turned off

Currently selected device family:

Stratix III

How will you be using the dual port ram?

With two read/write ports

How do you want to specify the memory size?

As a number of words

How many 8-bit words of memory?

16

Use different data widths on different ports

Not selected

How wide should the 'q_a' output bus be?

13

What should the memory block type be?

M9K

Set the maximum block depth to

Auto

Which clocking method do you want to use?

Single clock

Create 'rden_a' and 'rden_b' read enable signals

Not selected

Byte Enable Ports

Not selected

Which ports should be registered?

All write input ports and read output ports

Create one clock enable signal for each signal

Not selected

Create an 'aclr' asynchronous clear for the registered

ports

Not selected

Mixed Port Read-During-Write for Single Input

Clock RAM

Old memory contents appear

Port A Read-During-Write Option

New Data

Port B Read-During-Write Option

Old Data

Do you want to specify the initial content of the

memory?

Not selected

UG-01068

2014.12.17

Generating the ALTECC_ENCODER and ALTECC_DECODER with the RAM: 2-PORT IP

Core

5-3

Design Example

Altera Corporation