Read-during-write, Read-during-write -11 – Altera Internal Memory (RAM and ROM) IP Core User Manual

Page 21

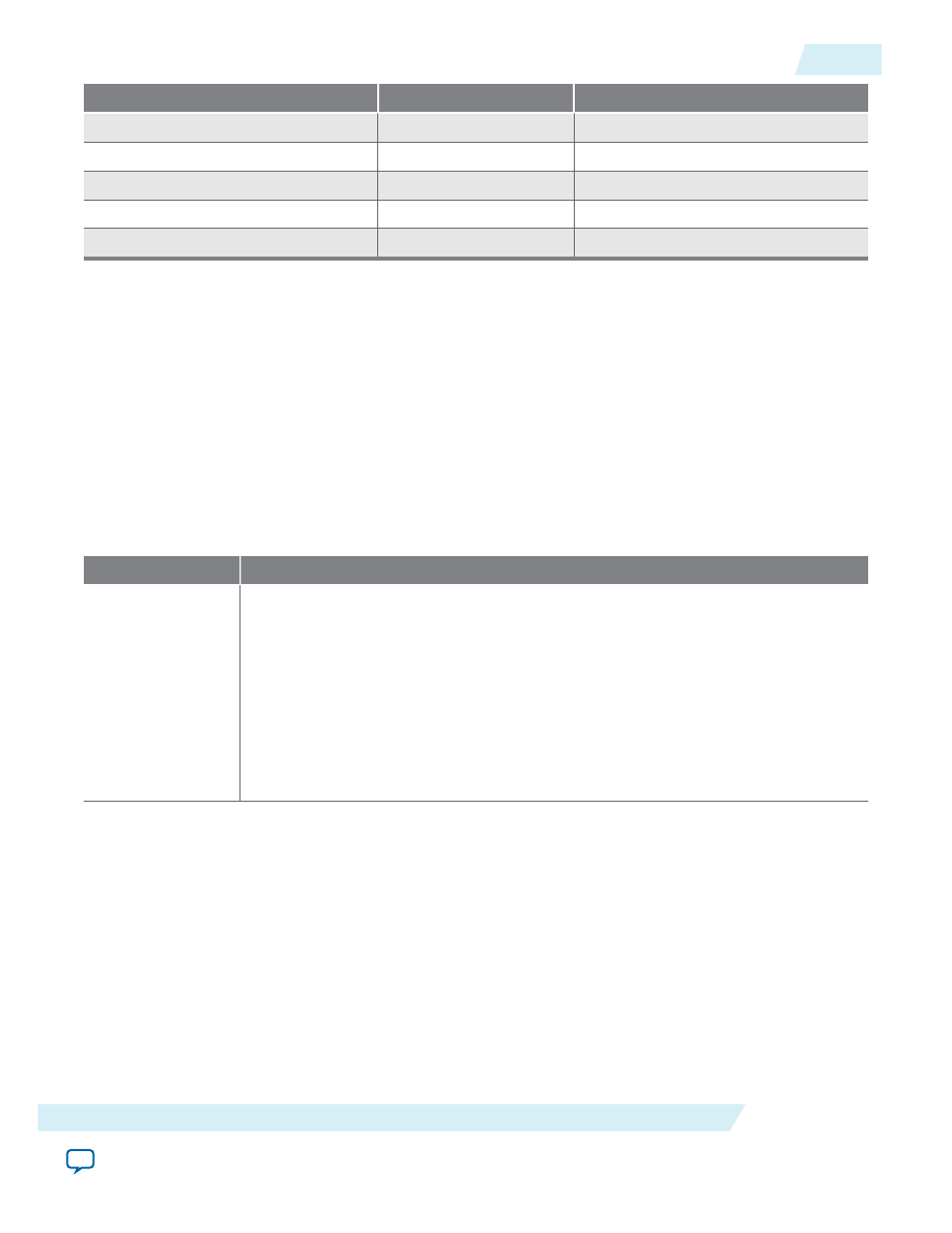

Memory Modes

M9K, M144K, M10K, M20K

MLAB

Simple dual-port RAM

Supported

—

True dual-port RAM

Supported

—

Tri-port RAM

Supported

—

Single-port ROM

Supported

—

Dual-port ROM

Supported

—

If you create the read-enable port and perform a write operation (with the read enable port deasserted),

the data output port retains the previous values that are held during the most recent active read enable. If

you activate the read enable during a write operation, or if you do not create a read-enable signal, the

output port shows the new data being written, the old data at that address, or a “Don't Care” value when

read-during-write occurs at the same address location.

Read-During-Write

The read-during-write (RDW) occurs when a read and a write target the same memory location at the

same time.

Table 3-8: RDW Operation

This table lists the RDW operations.

RDW Operation

Description

Same-Port RDW The same-port RDW occurs when the input and output of the same port access the

same address location with the same clock. The same-port RDW has the following

output choices:

• New Data—New data is available on the rising edge of the same clock cycle on

which it was written.

• Old Data—The RAM outputs reflect the old data at that address before the write

operation proceeds. Old Data is not supported for M10K and M20K memory

blocks in single-port RAM and true dual-port RAM.

• Don't Care—The RAM outputs “don't care” values for the RDW operation.

UG-01068

2014.12.17

Read-During-Write

3-11

Embedded Memory Functional Description

Altera Corporation