Altera Internal Memory (RAM and ROM) IP Core User Manual

Page 33

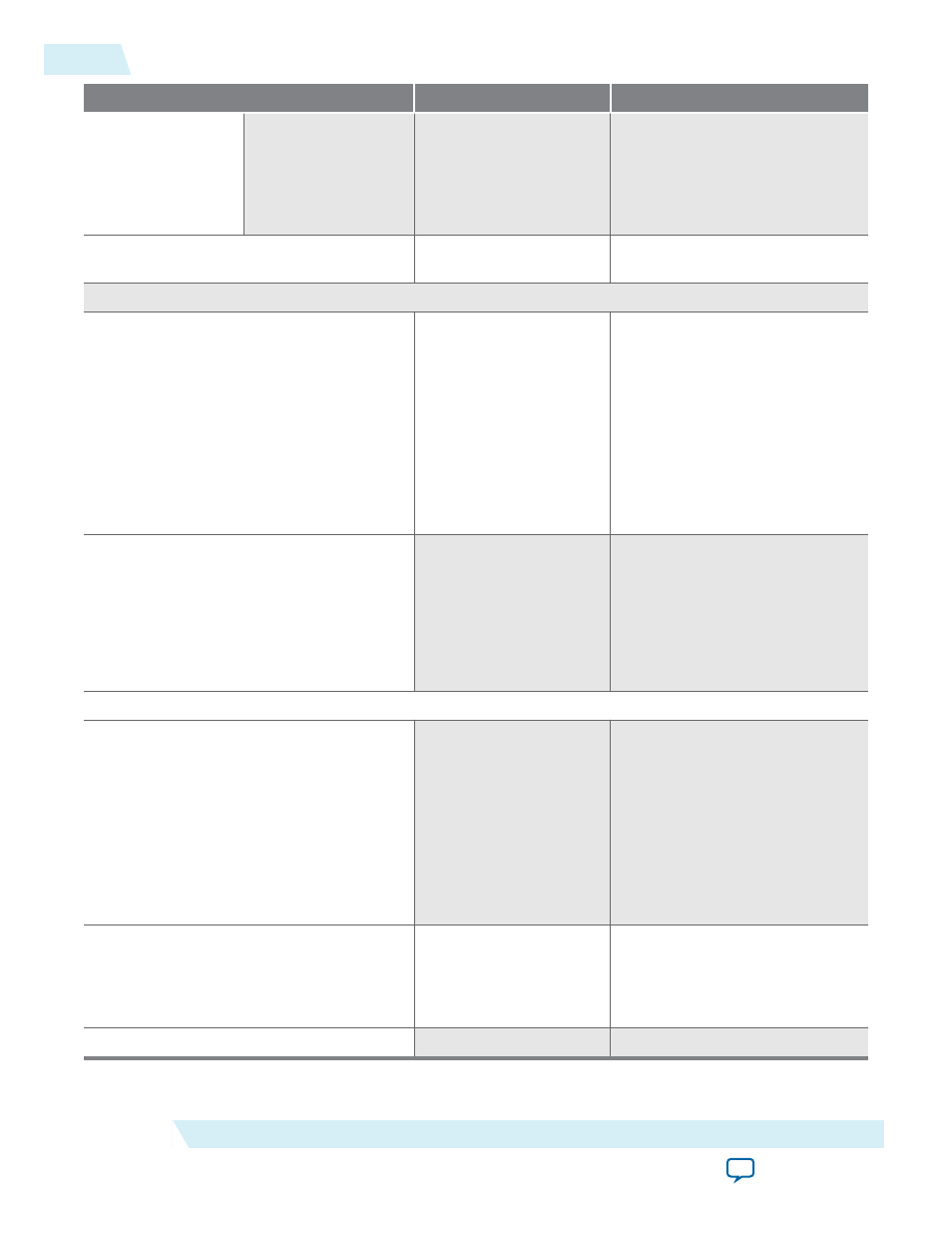

Parameter

Legal Values

Description

More Options

‘q’ port

On/Off

Turn on this option for the ‘q’

port to be affected by the

asynchronous clear signal. The

disabled ports are not affected

by the asynchronous clear

signal.

Create a ‘rden’ read enable signal

On/Off

Specifies whether to create a

read enable signal.

Parameter Settings: Read During Write Option

What should the q output be when reading

from a memory location being written to?

New data, Don’t Care

Specifies the output behavior

when read-during-write occurs.

New Data—New data is

available on the rising edge of

the same clock cycle on which it

was written.

Don’t Care—The RAM outputs

“don't care” or “unknown”

values for read-during-write

operation.

Get x’s for write masked bytes instead of

old data when byte enable is used

On/Off

Turn on this option to obtain

‘X’ on the masked byte.

For M10K and M20K memory

block, this option is not

available if you specify New

Data as the output behavior

when RDW occurs.

Parameter Settings: Mem Init

Do you want to specify the initial content

of the memory?

•

No, leave it blank

• Yes, use this file for the

memory content data

Specifies the initial content of

the memory.

To initialize the memory to

zero, select No, leave it blank.

To use a memory initialization

file (.mif) or a hexadecimal

(Intel-format) file (.hex), select

Yes, use this file for the

memory content data.

Allow In-System Memory Content Editor

to capture and update content independ‐

ently of the system clock

On/Off

Specifies whether to allow In-

System Memory Content Editor

to capture and update content

independently of the system

clock.

The ‘Instance ID’ of this RAM is

None

Specifies the RAM ID.

4-8

RAM:1-Port IP Core Parameters

UG-01068

2014.12.17

Altera Corporation

Embedded Memory Signals and Parameters